# ΤΕΧΝΟΛΟΓΙΚΟ ΕΚΠΑΙΔΕΥΤΙΚΟ ΙΔΡΥΜΑ (Τ.Ε.Ι.) ΛΑΜΙΑΣ ΣΧΟΛΗ ΤΕΧΝΟΛΟΓΙΚΩΝ ΕΦΑΡΜΟΓΩΝ ΤΜΗΜΑ ΗΛΕΚΤΡΟΝΙΚΗΣ ΤΟΜΕΑΣ ΥΠΟΔΟΜΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ

# ΨΗΦΙΑΚΑ ΗΛΕΚΤΡΟΝΙΚΑ ΕΡΓΑΣΤΗΡΙΑΚΕΣ ΑΣΚΗΣΕΙΣ

Δρ. ΑΣΗΜΑΚΗΣ ΝΙΚΟΛΑΟΣ

ΛΑΜΙΑ ΣΕΠΤΕΜΒΡΙΟΣ 2007

#### **HEPIEXOMENA**

ΕΡΓΑΣΤΗΡΙΑΚΕΣ ΑΣΚΗΣΕΙΣ

Η ΠΛΑΚΕΤΑ ΕΡΓΑΣΤΗΡΙΟΥ LT345

ΥΛΟΠΟΙΗΣΗ ΨΗΦΙΑΚΩΝ ΚΥΚΛΩΜΑΤΩΝ ΜΕ ΧΡΗΣΗ ΟΛΟΚΛΗΡΩΜΕΝΩΝ ΚΥΚΛΩΜΑΤΩΝ

ΣΧΕΔΙΑΣΗ ΚΑΙ ΠΡΟΣΟΜΟΙΩΣΗ ΨΗΦΙΑΚΩΝ ΚΥΚΛΩΜΑΤΩΝ ΜΕ ΧΡΗΣΗ ΤΟΥ ΠΑΚΕΤΟΥ ΛΟΓΙΣΜΙΚΟΥ DESIGNLAB

ΒΙΒΛΙΟΓΡΑΦΙΑ

ΠΑΡΑΡΤΗΜΑ ΦΥΛΛΑ ΔΕΔΟΜΕΝΩΝ ΟΛΟΚΛΗΡΩΜΕΝΩΝ ΚΥΚΛΩΜΑΤΩΝ ΤΗΣ ΣΕΙΡΑΣ 74

#### ΕΡΓΑΣΤΗΡΙΑΚΕΣ ΑΣΚΗΣΕΙΣ

#### **HEPIEXOMENA**

- 1. ΟΙ ΒΑΣΙΚΕΣ ΛΟΓΙΚΕΣ ΠΥΛΕΣ ΝΟΤ, AND KAI OR

- 2. ΛΟΓΙΚΕΣ ΣΥΝΑΡΤΗΣΕΙΣ

- 3. ΟΙ ΛΟΓΙΚΕΣ ΠΥΛΕΣ NAND KAI NOR

- 4. ΛΟΓΙΚΈΣ ΠΎΛΕΣ ΠΟΛΛΑΠΛΏΝ ΕΙΣΟΔΏΝ

- 5. ΟΙ ΛΟΓΙΚΕΣ ΠΥΛΕΣ ΧΟR ΚΑΙ ΧΝΟΡ

- 6. ΑΠΛΟΠΟΙΗΣΗ ΛΟΓΙΚΩΝ ΣΥΝΑΡΤΗΣΕΩΝ ΜΕ ΧΑΡΤΕΣ KARNAUGH

- 7. ΣΥΝΔΥΑΣΤΙΚΑ ΚΥΚΛΩΜΑΤΑ

- 8. ΟΙΚΟΥΜΕΝΙΚΈΣ ΠΥΛΈΣ ΔΥΟ ΕΙΣΟΔΩΝ

- 9. ΟΙΚΟΥΜΕΝΙΚΈΣ ΠΥΛΈΣ ΠΟΛΛΑΠΛΩΝ ΕΙΣΟΔΩΝ

- 10. ΔΥΑΔΙΚΉ ΠΡΟΣΘΕΣΉ ΚΑΙ ΑΦΑΙΡΈΣΗ

- 11. ΑΠΟΚΩΔΙΚΟΠΟΙΗΤΕΣ ΑΠΟΠΛΕΚΤΕΣ

- 12. ΚΩΔΙΚΟΠΟΙΗΤΕΣ

- 13. ΠΟΛΥΠΛΕΚΤΕΣ

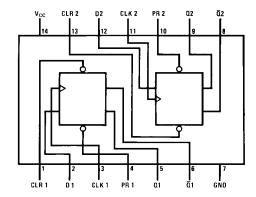

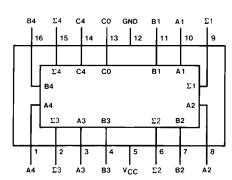

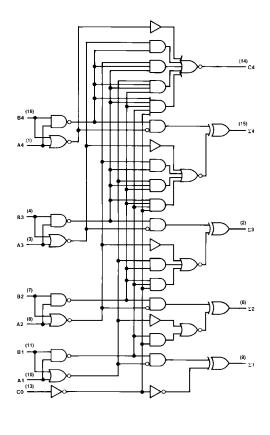

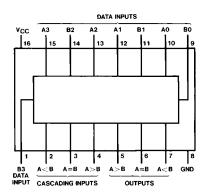

- 14. FLIP-FLOPS

- 15. ΚΑΤΑΧΩΡΗΤΕΣ

- 16. ΣΥΓΧΡΟΝΑ ΑΚΟΛΟΥΘΙΑΚΑ ΚΥΚΛΩΜΑΤΑ

- 17. ΑΠΑΡΙΘΜΗΤΕΣ

- 18. ΑΣΥΓΧΡΟΝΑ ΑΚΟΛΟΥΘΙΑΚΑ ΚΥΚΛΩΜΑΤΑ ΜΕ ΒΡΟΓΧΟ ΑΝΑΔΡΑΣΗΣ

- 19. ΑΣΥΓΧΡΟΝΑ ΑΚΟΛΟΥΘΙΑΚΑ ΚΥΚΛΩΜΑΤΑ ΜΕ ΜΑΝΤΑΛΩΤΕΣ

- 20. ΕΦΑΡΜΟΓΕΣ

# ΕΡΓΑΣΤΗΡΙΑΣΚΗ ΑΣΚΗΣΗ 1 ΟΙ ΒΑΣΙΚΕΣ ΛΟΓΙΚΕΣ ΠΥΛΕΣ ΝΟΤ, AND KAI OR

## Ι. Βασική Θεωρία

Η δίτιμη Άλγεβρα Boole είναι μία αλγεβρική δομή ορισμένη στο σύνολο τιμών  $B=\{0,1\}$  με δύο τελεστές + (OR) και  $\cdot$  (AND) με τους ακόλουθους Πίνακες Αληθείας:

| Х | у | x+y | х∙у |

|---|---|-----|-----|

| 0 | 0 | 0   | 0   |

| 0 | 1 | 1   | 0   |

| 1 | 0 | 1   | 0   |

| 1 | 1 | 1   | 1   |

Τα αξιώματα της Άλγεβρας Boole (αξιώματα Huntington) είναι:

- 1. Κλειστότητα ως προς τις πράξεις

- α. Κλειστότητα ως προς την πράξη + (OR)

- β. Κλειστότητα ως προς την πράξη · (AND)

- 2. Ουδέτερα στοιχεία πράξεων

- $\alpha. x+0=0+x=x$

- $\beta. x \cdot 1 = 1 \cdot x = x$

- 3. Αντιμεταθετική ιδιότητα

- $\alpha$ . x+y=y+x

- $\beta$ .  $x \cdot y = y \cdot x$

- 4. Επιμεριστική ιδιότητα

- $\alpha. x \cdot (y+z) = x \cdot y + x \cdot z$

- $\beta$ .  $x+(y\cdot z)=(x+y)\cdot(x+z)$

- 5. Μοναδικό Συμπλήρωμα (NOT)

- $\alpha$ . x+x'=1

- $\beta$ .  $x \cdot x' = 0$

- 6. Υπάρχουν τουλάχιστον δύο στοιχεία του συνόλου Β που είναι διαφορετικά μεταξύ τους

Τα θεωρήματα της Άλγεβρας Boole είναι:

- 1.  $\alpha$ . x+x=x

- $\beta$ .  $x \cdot x = x$

- 2.  $\alpha$ . x+1=1

- $\beta. x \cdot 0 = 0$

- 3. (x')'=x

- 4. Προσεταιριστική ιδιότητα

- $\alpha$ . x+y+z=x+(y+z)=(x+y)+z

- $\beta. x \cdot y \cdot z = x \cdot (y \cdot z) = (x \cdot y) \cdot z$

- 5. Θεώρημα απορρόφησης

- $\alpha$ .  $x+x\cdot y=x$

- $\beta. x \cdot (x+y)=x$

- 6. Θεωρήματα De Morgan

- $\alpha$ . (x+y)'=x',y'

- $\beta$ . (x.y)'=x'+y'

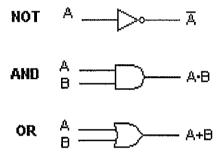

Οι βασικές πράξεις της Άλγεβρας Boole είναι οι πράξεις NOT, AND και OR. Στα ψηφιακά κυκλώματα οι τρεις αυτές πράξεις εκτελούνται από κυκλώματα που ονομάζονται λογικές πύλες. Κάθε πύλη παίρνει το όνομά της από την πράξη που εκτελεί. Ετσι έχουμε τις πύλες NOT, AND και OR. Η πύλη NOT έχει μία είσοδο και μία έξοδο, ενώ οι άλλες δύο (ή περισσότερες) εισόδους και μία έξοδο. Από την έξοδο κάθε πύλης μπορούν να τροφοδοτηθούν μία ή περισσότερες άλλες πύλες.

Οι είσοδοί και οι έξοδοι των πυλών μπορούν να πάρουν δύο μόνο τιμές, το λογικό "1" και το λογικό "0". Στη Θετική Λογική στο λογικό '1" αντιστοιχεί το υψηλότερο δυναμικό - High Level (π.χ. 5V), που συμβολίζεται και με το γράμμα H, ενώ στο λογικό ''0" αντιστοιχεί το χαμηλότερο δυναμικό - Low Level (π.χ. 0V) που συμβολίζεται και με το γράμμα L. Στην πράξη το λογικό ''1" αντιστοιχεί σε τάσεις 3.5V - 5V, ενώ το λογικό ''0" σε τάσεις 0V - 1.5V.

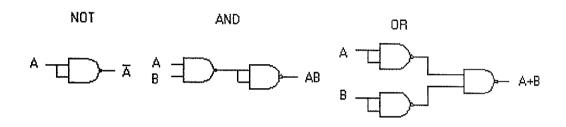

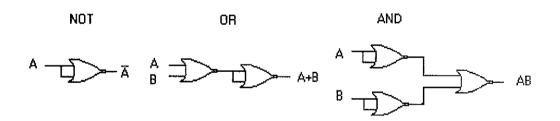

Τα σύμβολα των πυλών ΝΟΤ, ΑΝΟ δύο εισόδων και ΟR δύο εισόδων παρουσιάζονται στο παρακάτω σχήμα:

Τα σύμβολα των πυλών ΝΟΤ, ΑΝΟ και ΟR

Οι πίνακες αληθείας των πυλών ΝΟΤ, ΑΝΟ δύο εισόδων και ΟR δύο εισόδων παρουσιάζονται στον παρακάτω πίνακα:

Οι πίνακες αληθείας των πυλών ΝΟΤ, ΑΝD και ΟR

| NOT  |  |  |  |

|------|--|--|--|

| x x' |  |  |  |

| 0 1  |  |  |  |

| 1 0  |  |  |  |

| AND                |   |   |  |  |

|--------------------|---|---|--|--|

| x y <sub>x·y</sub> |   |   |  |  |

| 0                  | 0 | 0 |  |  |

| 0 1 0              |   |   |  |  |

| 1                  | 0 | 0 |  |  |

| 1                  | 1 | 1 |  |  |

| OR      |   |   |  |  |

|---------|---|---|--|--|

| x y x+y |   |   |  |  |

| 0       | 0 | 0 |  |  |

| 0       | 1 | 1 |  |  |

| 1       | 0 | 1 |  |  |

| 1       | 1 | 1 |  |  |

Η πύλη ΝΟΤ δίνει έξοδο "1" όταν η είσοδός της δεν είναι "1".

Η πύλη ΑΝΟ δίνει έξοδο "1" όταν όλες οι είσοδοί της είναι "1".

Η πύλη ΟΚ δίνει έξοδο "1" όταν τουλάχιστον μία από τις εισόδους της είναι "1".

#### Η. Πλακέτα Εργαστηρίου

1. Λογική πύλη ΝΟΤ

Να γίνει έλεγχος των λογικών πυλών ΝΟΤ της πλακέτας εργαστηρίου και να συμπληρώσετε τον πίνακα αληθείας.

2. Λογική πύλη ΑΝD δύο (2) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΑΝD δύο (2) εισόδων της πλακέτας εργαστηρίου και να συμπληρώσετε τον πίνακα αληθείας.

3. Λογική πύλη ΟΚ δύο (2) εισόδων

Να γίνει έλεγχος των λογικών πυλών δύο OR (2) εισόδων της πλακέτας εργαστηρίου και να συμπληρώσετε τον πίνακα αληθείας.

4. Λογική πύλη ΑΝΟ δύο (2) εισόδων με βραχυκυκλωμένες εισόδους

Να βραχυκυκλώσετε τις εισόδους μίας λογικής πύλης AND δύο (2) εισόδων και να επιβεβαιώσετε το θεώρημα της Άλγεβρας Boole:

$x \cdot x = x$

Να συμπληρώσετε τον πίνακα αληθείας:

| A | A·A |

|---|-----|

|   |     |

|   |     |

#### ΙΙΙ. Ολοκληρωμένα Κυκλώματα

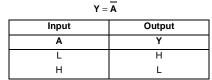

1. Λογική πύλη ΝΟΤ

Να γίνει έλεγχος των λογικών πυλών ΝΟΤ του ολοκληρωμένου κυκλώματος 7404 και να συμπληρώσετε τον πίνακα αληθείας.

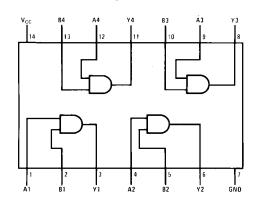

2. Λογική πύλη ΑΝΟ δύο (2) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΑΝΟ του ολοκληρωμένου κυκλώματος 7408 και να συμπληρώσετε τον πίνακα αληθείας.

3. Λογική πύλη ΟR δύο (2) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΟR του ολοκληρωμένου κυκλώματος 7432 και να συμπληρώσετε τον πίνακα αληθείας.

4. Λογική πύλη ΟΚ δύο (2) εισόδων με βραχυκυκλωμένες εισόδους

Να βραχυκυκλώσετε τις εισόδους μίας λογικής πύλης OR δύο (2) εισόδων του ολοκληρωμένου κυκλώματος 7432 και να επιβεβαιώσετε το θεώρημα της Άλγεβρας Boole: x+x=x

| A | A+A |

|---|-----|

|   |     |

|   |     |

## ΙΥ. Πακέτο Λογισμικού

### 1. Λογική πύλη ΝΟΤ

Να σχεδιάσετε μία πύλη ΝΟΤ.

Να σχεδιάσετε την κυματομορφή εισόδου και την κυματομορφή εξόδου.

## 2. Λογική πύλη ΑΝΟ δύο (2) εισόδων

Να σχεδιάσετε μία πύλη ΑΝΟ δύο (2) εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

## 3. Λογική πύλη ΟR δύο (2) εισόδων

Να σχεδιάσετε μία πύλη ΟR δύο (2) εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

### 4. Λογικές πύλες ΝΟΤ συνδεδεμένες σε σειρά

Να σχεδιάσετε δύο πύλες ΝΟΤ συνδεδεμένες σε σειρά.

Να σχεδιάσετε την κυματομορφή εισόδου και την κυματομορφή εξόδου.

Να επιβεβαιώσετε το θεώρημα της Άλγεβρας Boole:

(x')'=x

| Α | A' | (A')' |

|---|----|-------|

|   |    |       |

|   |    |       |

## ΕΡΓΑΣΤΗΡΙΑΣΚΗ ΑΣΚΗΣΗ 2 ΛΟΓΙΚΕΣ ΣΥΝΑΡΤΗΣΕΙΣ

## Ι. Βασική Θεωρία

Μία λογική συνάρτηση η μεταβλητών είναι μία έκφραση της Άλγεβρας Boole που περιλαμβάνει τις η μεταβλητές εισόδου, τους τελεστές των πράξεων της Άλγεβρας Boole και μία μεταβλητή εξόδου που είναι συνάρτηση των μεταβλητών εισόδου.

Ο τελεστής · (AND) μπορεί να παραλείπεται στις λογικές συναρτήσεις (για παράδειγμα, x·y=xy). Η προτεραιότητα των τελεστών στις λογικές συναρτήσεις είναι: (), NOT, AND, OR.

Η κάθε μία από τις η μεταβλητές εισόδου μπορεί να πάρει δύο μόνο τιμές, το λογικό "1" και το λογικό "0". Επομένως, οι δυνατοί συνδυασμοί των μεταβλητών εισόδου είναι 2<sup>η</sup>. Για κάθε συνδυασμό των μεταβλητών εισόδου, η μεταβλητή εξόδου παίρνει μία μόνο τιμή: το λογικό "1" ή το λογικό "0". Ο πίνακας αληθείας της λογικής συνάρτησης περιγράφει αυτή τη σχέση εισόδων-εξόδου.

## Παράδειγμα

Η λογική συνάρτηση Υ τριών μεταβλητών Α, Β και C έχει τον ακόλουθο πίνακα αληθείας:

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Ο πίνακας αληθείας έχει 8 (=2<sup>3</sup>) συνδυασμούς των 3 μεταβλητών εισόδου. Από τον πίνακα αληθείας προκύπτει ότι η συνάρτηση εξόδου είναι Y=1 όταν A=0 και (AND) B=0 και (AND) C=1 ή (OR)

A=1 και (AND) B=1 και (AND) C=0

Επομένως, η λογική συνάρτηση Υ γράφεται:

Y=A'B'C+ABC'

Το κύκλωμα που υλοποιεί τη λογική συνάρτηση αποτελείται από λογικές πύλες NOT, AND και OR που συνδέονται μεταξύ τους τηρώντας την προτεραιότητα των τελεστών (πραγματοποιούνται δηλαδή πρώτα οι πράξεις NOT, στη συνέχεια οι πράξεις AND και τέλος οι πράξεις OR).

Οι είσοδοι της λογικής συνάρτησης λαμβάνονται από διακόπτες εισόδου (switches) και η έξοδος της λογικής συνάρτησης κατευθύνεται σε ενδείκτη εξόδου (led).

## Η. Πλακέτα Εργαστηρίου

1. Θεώρημα απορρόφησης

Η λογική συνάρτηση Υ δύο μεταβλητών Α και Β έχει την ακόλουθη μορφή:

Y=A+AB

Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες NOT και πύλες AND και OR δύο εισόδων.

Να επιβεβαιώσετε το θεώρημα απορρόφησης της Άλγεβρας Boole:

$x+x\cdot y=x$

Να συμπληρώσετε τον πίνακα αληθείας:

| A | В | A+AB |

|---|---|------|

|   |   |      |

|   |   |      |

|   |   |      |

|   |   |      |

## 2. Επιμεριστική ιδιότητα

Δίνονται δύο λογικές συναρτήσεις Υ1 και Υ2 τριών μεταβλητών Α, Β και C:

Y1=A+BC

Y2=(A+B)+(A+C)

Να σχεδιάσετε και να υλοποιήσετε τα κυκλώματα χρησιμοποιώντας μόνο πύλες ΝΟΤ και πύλες ΑΝD και ΟR δύο εισόδων.

Να επιβεβαιώσετε την επιμεριστική ιδιότητα της Άλγεβρας Boole:

$x+(y\cdot z)=(x+y)\cdot(x+z)$

| Α | В | С | A+BC | (A+B)(A+C) |

|---|---|---|------|------------|

|   |   |   |      |            |

|   |   |   |      |            |

|   |   |   |      |            |

|   |   |   |      |            |

|   |   |   |      |            |

|   |   |   |      |            |

|   |   |   |      |            |

### ΙΙΙ. Ολοκληρωμένα Κυκλώματα

### 1. Επιμεριστική ιδιότητα

Δίνονται δύο λογικές συναρτήσεις Υ1 και Υ2 τριών μεταβλητών Α, Β και C:

Y1=A(B+C)

Y2=AB+AC

Να σχεδιάσετε και να υλοποιήσετε τα κυκλώματα χρησιμοποιώντας τα ολοκληρωμένα κυκλώματα 7408 και 7432.

Να επιβεβαιώσετε την επιμεριστική ιδιότητα της Άλγεβρας Boole:

$x \cdot (y+z) = x \cdot y + x \cdot z$

Να συμπληρώσετε τον πίνακα αληθείας:

| В | С | A(B+C) | AB+AC      |

|---|---|--------|------------|

|   |   |        |            |

|   |   |        |            |

|   |   |        |            |

|   |   |        |            |

|   |   |        |            |

|   |   |        |            |

|   |   |        |            |

|   | В | B C    | B C A(B+C) |

## 2. Λογική συνάρτηση

Η λογική συνάρτηση Y τριών μεταβλητών A, B και C έχει την ακόλουθη μορφή: Y = A + B'C

Να συμπληρώσετε τον πίνακα αληθείας:

| Α | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα ολοκληρωμένα κυκλώματα 7404, 7408 και 7432.

Να γίνει έλεγχος της λειτουργίας του κυκλώματος (να επιβεβαιώσετε τον πίνακα αληθείας).

### ΙΥ. Πακέτο Λογισμικού

1. Λογική συνάρτηση τριών μεταβλητών

Η λογική συνάρτηση Υ τριών μεταβλητών Α, Β και C έχει την ακόλουθη μορφή:

Y=AB+B'C

Να σχεδιάσετε το κύκλωμα και τις κυματομορφές εισόδου-εξόδου.

Να συμπληρώσετε τον πίνακα αληθείας:

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

2. Θεώρημα απορρόφησης

Η λογική συνάρτηση Υ δύο μεταβλητών Α και Β έχει την ακόλουθη μορφή:

Y=A(A+B)

Να σχεδιάσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες ΝΟΤ και πύλες ΑΝD και ΟR δύο εισόδων.

Να επιβεβαιώσετε το θεώρημα απορρόφησης της Άλγεβρας Boole:

$x \cdot (x+y)=x$

| Α | В | A(A+B) |

|---|---|--------|

|   |   |        |

|   |   |        |

|   |   |        |

|   |   |        |

## ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 3 ΟΙ ΛΟΓΙΚΈΣ ΠΥΛΈΣ NAND ΚΑΙ NOR

## Ι. Βασική Θεωρία

Τα σύμβολα των πυλών NAND δύο εισόδων και NOR δύο εισόδων παρουσιάζονται στο παρακάτω σχήμα:

NAND

$$\stackrel{A}{B}$$

$\longrightarrow$   $\overline{A \cdot B}$

Τα σύμβολα των πυλών ΝΑΝΟ και ΝΟΚ

Οι πίνακες αληθείας των πυλών ΝΑΝΟ δύο εισόδων και ΝΟΚ δύο εισόδων παρουσιάζονται στον παρακάτω πίνακα:

Οι πίνακες αληθείας των πυλών NAND και NOR

|   | NAND |       |  |  |  |

|---|------|-------|--|--|--|

| х | у    | (xy)' |  |  |  |

| 0 | 0    | 1     |  |  |  |

| 0 | 1    | 1     |  |  |  |

| 1 | 0    | 1     |  |  |  |

| 1 | 1    | 0     |  |  |  |

|   | NOR |        |  |  |  |  |

|---|-----|--------|--|--|--|--|

| Х | у   | (x+y)' |  |  |  |  |

| 0 | 0   | 1      |  |  |  |  |

| 0 | 1   | 0      |  |  |  |  |

| 1 | 0   | 0      |  |  |  |  |

| 1 | 1   | 0      |  |  |  |  |

Η λογική πύλη NAND είναι μία πύλη AND που ακολουθείται από μία πύλη NOT. Η πύλη NAND δίνει έξοδο "1"" όταν τουλάχιστον μία από τις εισόδους της είναι "0". Η λογική πύλη NOR είναι μία πύλη OR που ακολουθείται από μία πύλη NOT. Η πύλη NOR δίνει έξοδο "1" όταν όλες οι είσοδοι είναι "0".

#### Η. Πλακέτα Εργαστηρίου

## 1. Λογική πύλη NAND δύο (2) εισόδων

Να υλοποιήσετε μία πύλη NAND δύο (2) εισόδων χρησιμοποιώντας μία πύλη NAND τεσσάρων (4) εισόδων που διαθέτει η πλακέτα εργαστηρίου. Να βραχυκυκλώσετε ανά δύο τις τέσσερεις εισόδους της πύλης NAND τεσσάρων (4) εισόδων.

Να γίνει έλεγχος της λογικής πύλης ΝΑΝΟ δύο (2) εισόδων και να συμπληρώσετε τον πίνακα αληθείας.

#### 2. Λογική πύλη ΝΟΚ δύο (2) εισόδων

Να υλοποιήσετε μία πύλη NOR δύο (2) εισόδων χρησιμοποιώντας μία πύλη NOR τεσσάρων (4) εισόδων που διαθέτει η πλακέτα εργαστηρίου. Να βραχυκυκλώσετε ανά δύο τις τέσσερεις εισόδους της πύλης NOR τεσσάρων (4) εισόδων.

Να γίνει έλεγχος της λογικής πύλης ΝΟΚ δύο (2) εισόδων και να συμπληρώσετε τον πίνακα αληθείας.

#### ΙΙΙ. Ολοκληρωμένα Κυκλώματα

#### 1. Λογική πύλη ΝΑΝΟ δύο (2) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΝΑΝΟ του ολοκληρωμένου κυκλώματος 7400 και να συμπληρώσετε τον πίνακα αληθείας.

## 2. Θεώρημα De Morgan

Χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7400 να σχεδιάσετε και να υλοποιήσετε το κύκλωμα

Y1=(AB)'

Χρησιμοποιώντας τα ολοκληρωμένα κυκλώματα 7404 και 7432 να σχεδιάσετε και να υλοποιήσετε το κύκλωμα

Y2=A'+B'

Να επιβεβαιώσετε το θεώρημα De Morgan:

(x.y)'=x'+y'

| +B' | A'+B' | (AB)' | В | A |

|-----|-------|-------|---|---|

|     |       |       |   |   |

|     |       |       |   |   |

|     |       |       |   |   |

|     |       |       |   |   |

## ΙΥ. Πακέτο Λογισμικού

1. Λογική πύλη NOR δύο (2) εισόδων Να σχεδιάσετε μία πύλη NOR δύο (2) εισόδων. Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

2. Θεώρημα De Morgan

Να σχεδιάσετε τα κυκλώματα

Υ1=(A+B)'

Υ2=A'B'

Να σχεδιάσετε τις κυματομορφές εισόδων-εξόδων.

Να επιβεβαιώσετε το θεώρημα De Morgan:

(x+y)'=x'.y'

Να συμπληρώσετε τον πίνακα αληθείας:

| A | В | (A+B)' | A'B' |

|---|---|--------|------|

|   |   |        |      |

|   |   |        |      |

|   |   |        |      |

|   |   |        |      |

## ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 4 ΛΟΓΙΚΈΣ ΠΥΛΕΣ ΠΟΛΛΑΠΛΩΝ ΕΙΣΟΔΩΝ

### Ι. Βασική Θεωρία

Οι πύλες ΑΝD και ΟR υπάρχουν και με τη μορφή πολλαπλών εισόδων.

Οι πύλες ΑΝΟ και ΟR πολλαπλών εισόδων μπορούν να υλοποιηθούν συνδέοντας πολλές αντίστοιχες πύλες δύο εισόδων, γιατί ισχύει η προσεταιριστική ιδιότητα:

$$x+y+z=x+(y+z)=(x+y)+z$$

$$x \cdot y \cdot z = x \cdot (y \cdot z) = (x \cdot y) \cdot z$$

Ενδεικτικά, ο πίνακας αληθείας της λογικής πύλης ΑΝΟ τριών (3) εισόδων είναι:

| A | В | C | ABC |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 0   |

| 1 | 0 | 0 | 0   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 0 | 0   |

| 1 | 1 | 1 | 1   |

Οι πύλες NAND και NOR υπάρχουν και με τη μορφή πολλαπλών εισόδων. Οι πύλες NAND και NOR πολλαπλών εισόδων μπορούν να υλοποιηθούν συνδέοντας μία πύλη NOT στην έξοδο των αντίστοιχων πυλών AND και OR πολλαπλών εισόδων.

Ενδεικτικά, ο πίνακας αληθείας της λογικής πύλης ΝΟΚ τεσσάρων (4) εισόδων είναι:

| Α | В | С | D | (A+B+C+D)' |

|---|---|---|---|------------|

| 0 | 0 | 0 | 0 | 1          |

| 0 | 0 | 0 | 1 | 0          |

| 0 | 0 | 1 | 0 | 0          |

| 0 | 0 | 1 | 1 | 0          |

| 0 | 1 | 0 | 0 | 0          |

| 0 | 1 | 0 | 1 | 0          |

| 0 | 1 | 1 | 0 | 0          |

| 0 | 1 | 1 | 1 | 0          |

| 1 | 0 | 0 | 0 | 0          |

| 1 | 0 | 0 | 1 | 0          |

| 1 | 0 | 1 | 0 | 0          |

| 1 | 0 | 1 | 1 | 0          |

| 1 | 1 | 0 | 0 | 0          |

| 1 | 1 | 0 | 1 | 0          |

| 1 | 1 | 1 | 0 | 0          |

| 1 | 1 | 1 | 1 | 0          |

## Π. Πλακέτα Εργαστηρίου

1. Λογική πύλη ΑΝΟ τριών (3) εισόδων

Να υλοποιήσετε μία πύλη AND τριών (3) εισόδων χρησιμοποιώντας μία πύλη AND τεσσάρων (4) εισόδων που διαθέτει η πλακέτα εργαστηρίου. Να βραχυκυκλώσετε δύο από τις τέσσερεις εισόδους της πύλης AND τεσσάρων (4) εισόδων.

Να γίνει έλεγχος της λογικής πύλης ΑΝΟ τριών (3) εισόδων και να συμπληρώσετε τον πίνακα αληθείας.

2. Λογική πύλη ΟΚ τεσσάρων (4) εισόδων

Να υλοποιήσετε μία πύλη ΟR τεσσάρων (4) εισόδων που διαθέτει η πλακέτα εργαστηρίου. Να γίνει έλεγχος της λογικής πύλης ΟR τεσσάρων (4) εισόδων και να συμπληρώσετε τον πίνακα αληθείας.

3. Λογική πύλη NAND τριών (3) εισόδων

Να υλοποιήσετε μία πύλη NAND τριών (3) εισόδων χρησιμοποιώντας μία πύλη NAND τεσσάρων (4) εισόδων που διαθέτει η πλακέτα εργαστηρίου. Να βραχυκυκλώσετε δύο από τις τέσσερεις εισόδους της πύλης NAND τεσσάρων (4) εισόδων.

Να γίνει έλεγχος της λογικής πύλης ΝΑΝΟ τριών (3) εισόδων και να συμπληρώσετε τον πίνακα αληθείας.

4. Λογική πύλη ΝΟΚ τεσσάρων (4) εισόδων

Να υλοποιήσετε μία πύλη NOR τεσσάρων (4) εισόδων που διαθέτει η πλακέτα εργαστηρίου. Να γίνει έλεγχος της λογικής πύλης NOR τεσσάρων (4) εισόδων και να συμπληρώσετε τον πίνακα αληθείας.

5. Προσεταιριστική ιδιότητα

Να σχεδιάσετε και να υλοποιήσετε τα κυκλώματα

Y1=A+B+C

Y2=A+(B+C)

Y3 = (A + B) + C

Να επιβεβαιώσετε την προσεταιριστική ιδιότητα:

x+y+z=x+(y+z)=(x+y)+z

| A | В | С | A+B+C  | A+(B+C) | (A±D)±C |

|---|---|---|--------|---------|---------|

|   |   |   | 71.0.0 | Ar(D(C) | (A+B)+C |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        |         |         |

|   |   |   |        | L       |         |

#### ΙΙΙ. Ολοκληρωμένα Κυκλώματα

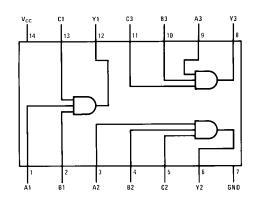

1. Λογική πύλη ΑΝΟ τριών (3) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΑΝD του ολοκληρωμένου κυκλώματος 7411 και να συμπληρώσετε τον πίνακα αληθείας.

2. Λογική πύλη NAND τριών (3) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΝΑΝΟ του ολοκληρωμένου κυκλώματος 7410 και να συμπληρώσετε τον πίνακα αληθείας.

3. Λογική πύλη ΝΟΚ τριών (3) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΝΟΡ του ολοκληρωμένου κυκλώματος 7427 και να συμπληρώσετε τον πίνακα αληθείας.

4. Λογική πύλη NAND τεσσάρων (4) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΝΑΝΟ του ολοκληρωμένου κυκλώματος 7420 και να συμπληρώσετε τον πίνακα αληθείας.

5. Λογική πύλη NAND οκτώ (8) εισόδων

Να γίνει έλεγχος της λογικής πύλης ΝΑΝΟ του ολοκληρωμένου κυκλώματος 7430.

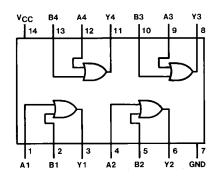

6. Προσεταιριστική ιδιότητα

Χρησιμοποιώντας τα ολοκληρωμένα κυκλώματα 7408 και 7411 να σχεδιάσετε τα κυκλώματα:

$Y1=A \cdot B \cdot C$

$Y2=A \cdot (B \cdot C)$

$Y3=(A \cdot B) \cdot C$

Να επιβεβαιώσετε την προσεταιριστική ιδιότητα:

$x \cdot y \cdot z = x \cdot (y \cdot z) = (x \cdot y) \cdot z$

| Α | В | С     | A•B•C | A• (B•C) | (A • B) • C |

|---|---|-------|-------|----------|-------------|

|   |   |       |       |          |             |

|   |   |       |       |          |             |

|   |   |       |       |          |             |

|   |   | #4 ## |       |          |             |

|   |   |       |       |          |             |

|   |   |       |       |          |             |

|   |   |       |       |          |             |

# ΙΥ. Πακέτο Λογισμικού

1. Λογική πύλη NAND τεσσάρων (4) εισόδων

Να σχεδιάσετε μία πύλη ΝΑΝΟ τεσσάρων (4) εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

2. Λογική πύλη NAND τεσσάρων (4) εισόδων με πύλες ΑΝD και ΝΟΤ

Να σχεδιάσετε μία πύλη ΝΑΝΟ τεσσάρων (4) εισόδων.

Να σχεδιάσετε μία πύλη ΑΝΟ τεσσάρων (4) εισόδων με μία πύλη ΝΟΤ στην έξοδο.

Να σχεδιάσετε τις κυματομορφές εισόδων-εξόδων.

Να επιβεβαιώσετε ότι μία πύλη ΝΑΝΟ τεσσάρων εισόδων μπορεί να υλοποιηθεί συνδέοντας μία πύλη ΝΟΤ στην έξοδο μίας πύλης ΑΝΟ τεσσάρων εισόδων.

3. Η προσεταιριστική ιδιότητα δεν ισχύει για την πύλη ΝΑΝΟ

Να σχεδιάσετε τα κυκλώματα

Y1=(ABC)

Y2=((AB)'C)'

Να σχεδιάσετε τις κυματομορφές εισόδων-εξόδων.

Να επιβεβαιώσετε ότι

Y1≠Y2

δηλαδή ότι η προσεταιριστική ιδιότητα δεν ισχύει για την πύλη NAND.

4. Η προσεταιριστική ιδιότητα δεν ισχύει για την πύλη NOR

Να σχεδιάσετε τα κυκλώματα

Y1=(A+B+C)

Y2=((A+B)'+C)'

Να σχεδιάσετε τις κυματομορφές εισόδων-εξόδων.

Να επιβεβαιώσετε ότι

Y1≠Y2

δηλαδή ότι η προσεταιριστική ιδιότητα δεν ισχύει για την πύλη NOR.

## ΕΡΓΑΣΤΗΡΙΑΚΗ ΑΣΚΗΣΗ 5 ΟΙ ΛΟΓΙΚΕΣ ΠΥΛΕΣ ΧΟR ΚΑΙ ΧΝΟR

### Ι. Βασική Θεωρία

Τα σύμβολα των πυλών XOR δύο εισόδων και XNOR δύο εισόδων παρουσιάζονται στο παρακάτω σχήμα:

XOR

$$\stackrel{A}{=}$$

$\longrightarrow$  A $\oplus$ E

Τα σύμβολα των πυλών ΧΟΡ και ΧΝΟΡ

Οι πίνακες αληθείας των πυλών ΧΟΡ και ΧΝΟΡ δύο εισόδων παρουσιάζονται στον παρακάτω πίνακα:

Οι πίνακες αληθείας των πυλών ΧΟΚ και ΧΝΟΚ

| XOR |   |     |  |  |  |

|-----|---|-----|--|--|--|

| х   | у | х⊕у |  |  |  |

| 0   | 0 | 0   |  |  |  |

| 0   | 1 | 1   |  |  |  |

| 1   | 0 | 1   |  |  |  |

| 1   | 1 | 0   |  |  |  |

| XNOR |   |     |  |  |

|------|---|-----|--|--|

| х    | у | хФу |  |  |

| 0    | 0 | 1   |  |  |

| 0    | 1 | 0   |  |  |

| 1    | 0 | 0   |  |  |

| 1    | 1 | 1   |  |  |

Η πύλη XOR δίνει έξοδο "1" όταν οι είσοδοί της είναι σε διαφορετική κατάσταση. Η πύλη XNOR δίνει έξοδο "1" όταν οι είσοδοί της είναι στην ίδια κατάσταση.

Oι λογικές συναρτήσεις των πυλών XOR και XNOR δύο εισόδων είναι:  $x \oplus y = xy' + x'y$   $(x \oplus y)' = xy + x'y'$

Oι λογικές συναρτήσεις των πυλών XOR και XNOR δύο εισόδων συνδέονται με τη σχέση:  $x \oplus y = (x \odot y)'$

#### Η. Πλακέτα Εργαστηρίου

### 1. Λογική πύλη ΧΟΚ δύο (2) εισόδων

Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα μίας πύλης ΧΟR δύο εισόδων:

x⊕y=xy'+x'y

Να γίνει έλεγχος της λογικής πύλης ΧΟΡ δύο (2) εισόδων και να συμπληρώσετε τον πίνακα αληθείας.

## 2. Λογική πύλη ΧΝΟΚ δύο (2) εισόδων

Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα μίας πύλης ΧΝΟΚ δύο εισόδων:

$x \cdot y=xy+x'y'$

Να γίνει έλεγχος της λογικής πύλης ΧΝΟΚ δύο (2) εισόδων και να συμπληρώσετε τον πίνακα αληθείας.

#### ΙΙΙ. Ολοκληρωμένα Κυκλώματα

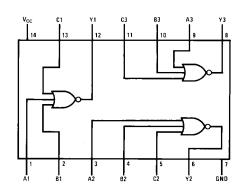

#### 1. Λογική πύλη ΧΟΡ δύο (2) εισόδων

**Να γίνει έλεγχος των λογικών πυλών** ΧΟΚ του ολοκληρωμένου κυκλώματος 7486 και να συμπληρώσετε τον πίνακα αληθείας.

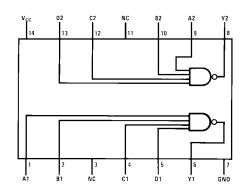

## 2. Λογική πύλη ΧΝΟΚ δύο (2) εισόδων

Να γίνει έλεγχος των λογικών πυλών ΧΝΟΚ του ολοκληρωμένου κυκλώματος 74266 και να συμπληρώσετε τον πίνακα αληθείας.

Να επιβεβαιώσετε ότι οι λογικές συναρτήσεις των πυλών ΧΟR και ΧΝΟR δύο εισόδων συνδέονται με τη σχέση:

$x \oplus y = (x \odot y)'$

### 3. Κύκλωμα παραγωγής bit άρτιας ισοτιμίας

Η λογική συνάρτηση του κυκλώματος παραγωγής bit άρτιας ισοτιμίας τριών bit είναι:

$P=A\oplus B\oplus C=(A\oplus B)\oplus C$

Να υλοποιήσετε το κύκλωμα χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7486. Να συμπληρώσετε τον πίνακα αληθείας:

| Α | В | С | Ρ (άρτια ισοτιμία) |

|---|---|---|--------------------|

| 0 | 0 | 0 |                    |

| 0 | 0 | 1 |                    |

| 0 | 1 | 0 |                    |

| 0 | 1 | 1 |                    |

| 1 | 0 | 0 |                    |

| 1 | 0 | 1 |                    |

| 1 | 1 | 0 |                    |

| 1 | 1 | 1 |                    |

## ΙΥ. Πακέτο Λογισμικού

1. Λογική πύλη ΧΟΚ δύο (2) εισόδων

Να σχεδιάσετε μία πύλη ΧΟΚ δύο (2) εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

Να συμπληρώσετε τον πίνακα αληθείας.

2. Κύκλωμα παραγωγής bit περιττής ισοτιμίας

Η λογική συνάρτηση του κυκλώματος παραγωγής bit περιττής ισοτιμίας τριών bit είναι:  $P=(A\oplus B\oplus C)$ '

Να σχεδιάσετε το κύκλωμα.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

| A | В | С | Ρ (περιττή ισοτιμία) |

|---|---|---|----------------------|

|   |   |   |                      |

|   |   |   |                      |

|   |   |   |                      |

|   |   |   |                      |

|   |   |   |                      |

|   |   |   |                      |

## ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 6 ΑΠΛΟΠΟΙΉΣΗ ΛΟΓΙΚΩΝ ΣΥΝΑΡΤΉΣΕΩΝ ΜΕ ΧΑΡΤΈΣ KARNAUGH

#### Ι. Βασική Θεωρία

**Ελάχιστοι όροι** μίας λογικής συνάρτησης ονομάζονται όλα τα γινόμενα όλων των όρων της συνάρτησης, όπου ο κάθε όρος (μεταβλητή) εμφανίζεται στην κανονική (αν έχει τιμή "1") ή στην συμπληρωματική του μορφή (αν έχει τιμή "0").

**Μέγιστοι όροι** μίας λογικής συνάρτησης ονομάζονται όλα τα αθροίσματα όλων των όρων της συνάρτησης, όπου ο κάθε όρος (μεταβλητή) εμφανίζεται στην κανονική (αν έχει τιμή "0") ή στην συμπληρωματική του μορφή (αν έχει τιμή "1").

Μία λογική συνάρτηση n μεταβλητών έχει  $2^n$  ελάχιστους όρους και  $2^n$  μέγιστους όρους. Οι ελάχιστοι όροι συμβολίζονται με mi και οι μέγιστοι όροι συμβολίζονται με Mi όπου  $i=0,1,...,2^{n}-1$ . Προφανώς ισχύει ότι mi'=Mi όπου  $i=0,1,...,2^{n}-1$ .

Κάθε λογική συνάρτηση μπορεί να εκφρασθεί ως άθροισμα ελάχιστων όρων (ΣΠ μορφή) και ως γινόμενο μέγιστων όρων (ΠΣ μορφή). Αυτές οι δύο μορφές έκφρασης των συναρτήσεων ονομάζονται Κανονικές Μορφές.

Για παράδειγμα, η συνάρτηση Y=Y(x,y,z) τριών μεταβλητών x, y και z όπου x είναι το περισσότερο σημαντικό ψηφίο (Most Significant Bit - MSB) και z είναι το λιγότερο σημαντικό ψηφίο (Least Significant Bit - LSB) έχει οκτώ ελάχιστους όρους και οκτώ μέγιστους όρους  $(2^3=8)$ . Ο πίνακας αληθείας της συνάρτησης είναι:

| Х | у | Z | Y | Ελάχιστοι όροι | Μέγιστοι Οροι |

|---|---|---|---|----------------|---------------|

| 0 | 0 | 0 | 0 | m0=x'y'z'      | M0=x+y+z      |

| 0 | 0 | 1 | 1 | m1=x'y'z       | M1=x+y+z'     |

| 0 | 1 | 0 | 0 | m2=x'yz'       | M2=x+y'+z     |

| 0 | 1 | 1 | 0 | m3=x'yz        | M3=x+y'+z'    |

| 1 | 0 | 0 | 1 | m4=xy'z'       | M4=x'+y+z     |

| 1 | 0 | 1 | 0 | m5=xy'z        | M5=x'+y+z'    |

| 1 | 1 | 0 | 0 | m6=xyz'        | M6=x'+y'+z    |

| 1 | 1 | 1 | 1 | m7=xyz         | M7=x'+y'+z'   |

Τότε οι δύο κανονικές μορφές της συνάρτησης Υ είναι:

- ΣΠ μορφή: η συνάρτηση Υ ως άθροισμα ελάχιστων όρων

$Y=x'y'z+xy'z'+xyz=m1+m4+m7=\Sigma(1,4,7)$

- ΠΣ μορφή: η συνάρτηση Υ ως γινόμενο μέγιστων όρων

$Y=(x+y+z)(x+y'+z)(x+y'+z')(x'+y+z')(x'+y+z)=M0 M2 M3 M5 M6=\Pi(0,2,3,5,6)$

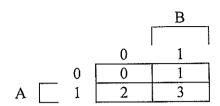

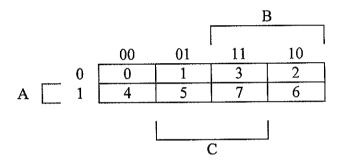

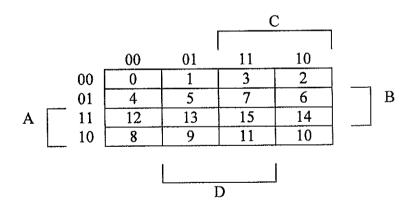

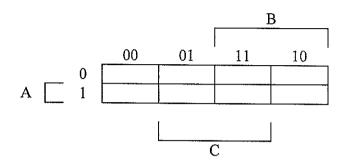

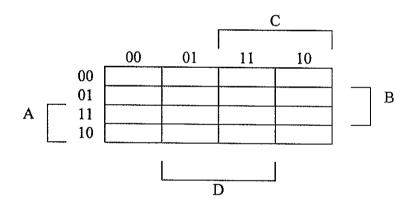

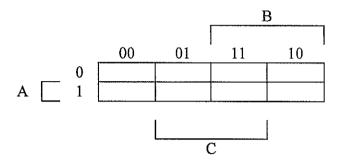

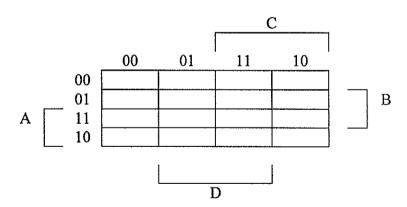

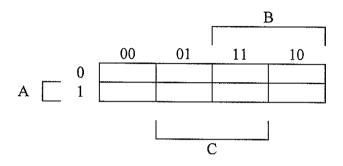

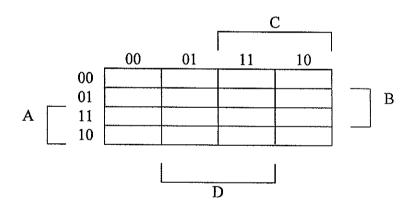

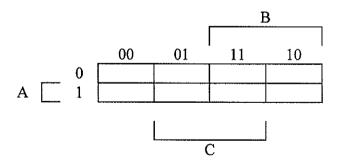

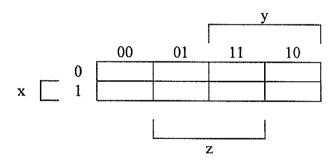

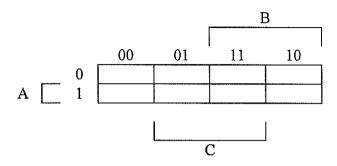

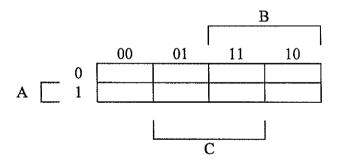

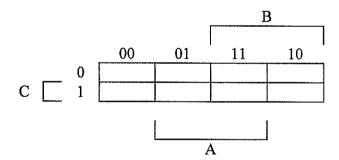

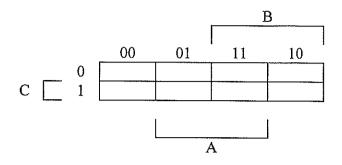

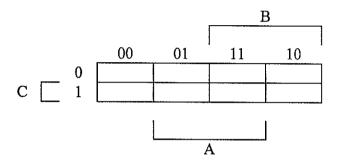

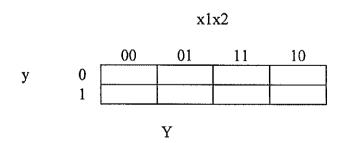

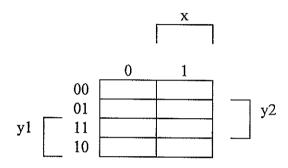

Οι χάρτες Karnaugh είναι ένας τρόπος αναπαράστασης των λογικών συναρτήσεων. Ο χάρτης Karnaugh είναι ένας πίνακας όπου το κάθε τετράγωνο αναπαριστά ένα συνδυασμό των μεταβλητών, δηλαδή κάθε τετράγωνο ενός χάρτη Karnaugh αντιστοιχεί σε έναν ελάχιστο όρο της λογικής συνάρτησης που αναπαριστά. Οι θέσεις των ελαχίστων όρων στους χάρτες Karnaugh συναρτήσεων δύο, τριών και τεσσάρων μεταβλητών παρουσιάζονται παρακάτω:

(α) Χάρτης Karnaugh δύο μεταβλητών

(β) Χάρτης Karnaugh τριών μεταβλητών

(γ) Χάρτης Karnaugh τεσσάρων μεταβλητών

Χάρτες Karnaugh

Η αναπαράσταση μίας λογικής συνάρτησης με χάρτη Karnaugh γίνεται θέτοντας "1" σε κάθε τετράγωνο του χάρτη Karnaugh που αντιστοιχεί σε ελάχιστο όρο όπου η συνάρτηση έχει τιμή "1" και θέτοντας "0" (ή τίποτα) σε κάθε τετράγωνο του χάρτη Karnaugh που αντιστοιχεί σε ελάχιστο όρο όπου η συνάρτηση έχει τιμή "0". Σε πολλές περιπτώσεις, μερικοί συνδυασμοί των μεταβλητών εισόδου δεν έχουν νόημα και δεν πρόκειται να συμβούν. Αυτοί οι συνδυασμοί καλούνται συνθήκες αδιαφορίας γιατί δεν ενδιαφέρει η τιμή της συνάρτησης για τους συνδυασμούς αυτούς. Στον πίνακα αληθείας και στον χάρτη Karnaugh μίας τέτοιας συνάρτησης οι τιμές της συνάρτησης στις συνθήκες αδιαφορίας συμβολίζονται με Χ.

Για παράδειγμα, η λογική συνάρτηση

Y=A'BC+AB'C'+ABC

έχει τον ακόλουθο χάρτη Karnaugh:

Χάρτης Karnaugh της συνάρτησης Y=A'BC+AB'C'+ABC

Για να απλοποιήσουμε μία λογική συνάρτηση χρησιμοποιώντας χάρτη Karnaugh, ακολουθούμε τα εξής βήματα:

- Γράφουμε τη συνάρτηση με μορφή αθροίσματος ελαχίστων όρων.

- Τοποθετούμε τους όρους της συνάρτησης στον χάρτη Karnaugh σημειώνοντας με "1" το αντίστοιχο τετράγωνο.

- Δημιουργούμε ομάδες με "1" των 2, 4, 8, 16 μελών από γειτονικά τετράγωνα (οριζόντια ή κάθετα, συνεχόμενα ή αναδιπλούμενα, αλλά όχι διαγώνια). Προσπαθούμε να δημιουργούμε όσο το δυνατόν μεγαλύτερες ομάδες. Κάθε "1" μπορεί να συμμετέχει σε περισσότερες από μία ομάδες.

- Ξαναγράφουμε τη συνάρτηση με όρους τους ελεύθερους όρους που πιθανόν να υπάρχουν και τις ομάδες (παραλείποντας τις μεταβλητές που μέσα στην ομάδα αλλάζουν τιμή).

Για την απλοποίηση μίας τέτοιας συνάρτησης με χάρτη Karnaugh η τιμή "Χ" μπορεί να θεωρηθεί είτε ως "0" ειτε ως "1", ανάλογα με τι συμφέρει, δηλαδή με το ποιά από τις δύο τιμές δίνει την απλούστερη έκφραση. Τα "Χ" επιτρέπεται να τα ομαδοποιηθούν με τους "1" ή να μην ληφθούν καθόλου υπόψη.

Παράδειγμα 1.

Δίνεται η συνάρτηση

Y=A(B'C+BCD')+ABCD

Κάνοντας πράξεις, η συνάρτηση γράφεται:

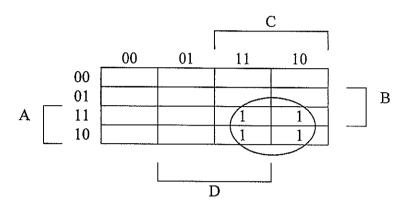

Y=AB'C+ABCD'+ABCD=AB'CD+AB'CD'+ABCD'+ABCD= $\Sigma$ (10,11,14,15)

Ο δεύτερος και ο τρίτος όρος αντιστοιχούν στα τετράγωνα 14 και 15 αντίστοιχα του χάρτη Karnaugh. Ο πρώτος όρος είναι ελλιπής (αφού λείπει η μεταβλητή D) και αντιστοιχεί στα τετράγωνα 10 και 11 του χάρτη Karnaugh. Ο χάρτης Karnaugh της συνάρτησης είναι:

Χάρτης Karnaugh της συνάρτησης Y=A(B'C+BCD')+ABCD

Οι τέσσερις "1" αποτελούν μία ομάδα (τετράδα). Μέσα στην ομάδα αυτή αλλάζουν τιμή οι μεταβλητές Β και D, οπότε παραλείπονται. Οι μεταβλητές Α και C έχουν τιμή "1". Επομένως, η απλοποιημένη συνάρτηση είναι: Y=AC

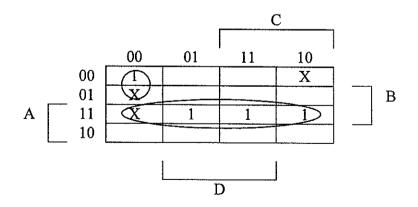

# Παράδειγμα 2. Δίνεται η συνάρτηση Y=A'B'C'D'+ABD+ABCD' με αδιάφορους όρους A'B'CD' και BC'D' Ο χάρτης Karnaugh της συνάρτησης είναι:

Χάρτης Karnaugh της συνάρτησης Y=A'B'C'D'+ABD+ABCD' με αδιάφορους όρους A'B'CD' και BC'D'

Επομένως, η απλοποιημένη συνάρτηση είναι: Y=AB+A'C'D' όπου ο πρώτος όρος αντιστοιχεί στην ομάδα των τεσσάρων όρων και ο δεύτερος στην ομάδα των δύο όρων.

## ΙΙ. Πλακέτα Εργαστηρίου

1. Απλοποίηση συνάρτησης τριών μεταβλητών με χάρτη Karnaugh Δίνεται η συνάρτηση τριών μεταβλητών  $Y(A,B,C)=\Sigma(0,2,3,4,6)$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να υλοποιήσετε το κύκλωμα.

2. Απλοποίηση συνάρτησης τεσσάρων μεταβλητών με χάρτη Karnaugh Δίνεται η συνάρτηση τεσσάρων μεταβλητών Y(A,B,C,D)=A'B'C'D'+AB'C'D'+A'B'CD'+AB'CD' Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης. Να απλοποιήσετε τη λογική συνάρτηση και να υλοποιήσετε το κύκλωμα.

#### ΙΙΙ. Ολοκληρωμένα Κυκλώματα

1. Απλοποίηση συνάρτησης τριών μεταβλητών με χάρτη Karnaugh Δίνεται η συνάρτηση τριών μεταβλητών

Y(A,B,C)=AB+B'C

με αδιάφορο όρο τον Α'ΒC

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα κατάλληλα ολοκληρωμένα κυκλώματα.

2. Απλοποίηση συνάρτησης τεσσάρων μεταβλητών με χάρτη Karnaugh

Δίνεται η συνάρτηση τεσσάρων μεταβλητών

Y(A,B,C)=C'D'(A'B+AB')+BC'D+AD'(BC'+B'C)+ABCD'

με αδιάφορους όρους τους BCD

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα κατάλληλα ολοκληρωμένα κυκλώματα.

# ΙΥ. Πακέτο Λογισμικού

1. Απλοποίηση συνάρτησης τριών μεταβλητών με χάρτη Karnaugh Δίνεται η συνάρτηση τριών μεταβλητών  $Y(A,B,C)=\Sigma(2,3,4,5)$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης. Να απλοποιήσετε τη λογική συνάρτηση και να σχεδιάσετε το κύκλωμα. Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

2. Απλοποίηση συνάρτησης τεσσάρων μεταβλητών με χάρτη Karnaugh Δίνεται η συνάρτηση τεσσάρων μεταβλητών Y(A,B,C)=Π(1,3,5,7,9,11,12,13,14,15) Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης. Να απλοποιήσετε τη λογική συνάρτηση και να σχεδιάσετε το κύκλωμα. Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

## ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 7 ΣΥΝΔΥΑΣΤΙΚΑ ΚΎΚΛΩΜΑΤΑ

#### Ι. Βασική Θεωρία

Ενα Συνδυαστικό Κύκλωμα (ΣΚ) η εισόδων και m εξόδων περιγράφεται από m λογικές συναρτήσεις η μεταβλητών. Η κάθε μία από τις η μεταβλητές εισόδου μπορεί να πάρει δύο μόνο τιμές, το λογικό "1" και το λογικό "0". Επομένως, οι δυνατοί συνδυασμοί των μεταβλητών εισόδου είναι 2<sup>n</sup>. Για κάθε συνδυασμό των μεταβλητών εισόδου, η κάθε μία μεταβλητή εξόδου παίρνει μία μόνο τιμή: το λογικό "1" ή το λογικό "0". Ο πίνακας αληθείας της λογικής συνάρτησης περιγράφει αυτή τη σχέση εισόδων-εξόδου.

Για να σχεδιάσουμε ένα Συνδυαστικό Κύκλωμα ακολουθούμε τα εξής βήματα:

- Κατασκευάζουμε τον πίνακα αληθείας του Συνδυαστικού Κυκλώματος

- Γράφουμε τις λογικές συναρτήσεις των εξόδων συναρτήσει των εισόδων

- Απλοποιούμε τις συναρτήσεις χρησιμοποιώντας χάρτες Karnaugh

- Σχεδιάζουμε το κύκλωμα τηρώντας την προτεραιότητα των πράξεων

Κάθε Συνδυαστικό Κύκλωμα μπορεί να υλοποιηθεί χρησιμοποιώντας λογικές πύλες.

## Παράδειγμα

Να σχεδιαστεί ένα Συνδυαστικό Κύκλωμα (ΣΚ) που αναγνωρίζει αν ένας 3-bit αριθμός είναι μικρότερος από 3, χρησιμοποιώντας μόνο πύλες ΝΟΤ και πύλες ΑΝD και ΟR δύο εισόδων. Το ΣΚ έχει τρεις εισόδους Α, Β και C, που αποτελούν τη δυαδική αναπαράσταση ενός δεκαδικού αριθμού από το 0 έως και το 7 (θυμηθείτε ότι με 3 bit μπορούμε να μετρήσουμε  $2^3$ =8 αριθμούς) και μία έξοδο Υ. Η έξοδος του ΣΚ είναι "1" όταν το δεκαδικό ισοδύναμο του 3-bit δυαδικού αριθμού των εισόδων του ΣΚ είναι μικρότερο από 3.

Από την περιγραφή της λειτουργίας του ΣΚ κατασκευάζεται ο παρακάτω πίνακας αληθείας του ΣΚ:

Πίνακας Αληθείας του Συνδυαστικού Κυκλώματος

| δεκαδικός | Α | В | C | Y |

|-----------|---|---|---|---|

| 0         | 0 | 0 | 0 | 1 |

| 1         | 0 | 0 | 1 | 1 |

| 2         | 0 | 1 | 0 | 1 |

| 3         | 0 | 1 | 1 | 0 |

| 4         | 1 | 0 | 0 | 0 |

| 5         | 1 | 0 | 1 | 0 |

| 6         | 1 | 1 | 0 | 0 |

| 7         | 1 | 1 | 1 | 0 |

Από τον Πίνακα Αληθείας του ΣΚ προκύπτει ότι η συνάρτηση εξόδου του ΣΚ είναι Y=1 όταν

A=0 και (AND) B=0 και (AND) C=0

ή (OR)

A=0 και (AND) B=0 και (AND) C=1

ή(OR)

A=0 και (AND) B=1 και (AND) C=0

Epoménas,  $\eta$  sunárthsh exódon tou  $\Sigma K$  enrísketai we sunárthsh twn eisódwn tou  $\Sigma K$ : Y=A'B'C'+A'B'C+A'BC'

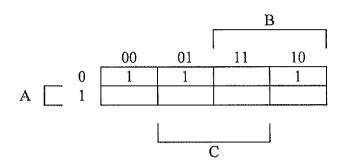

Ο χάρτης Karnaugh της συνάρτησης εξόδου του ΣΚ είναι:

Χάρτης Karnaugh της συνάρτησης Y=A'B'C'+A'B'C+A'BC'=A'B'+A'C'

Η απλοποιημένη συνάρτηση είναι:

Y=A'B'+A'C'

Η συνάρτηση γράφεται:

Y=A'B'+A'C'=A'(B'+C')=A'(BC)'=(A+BC)'

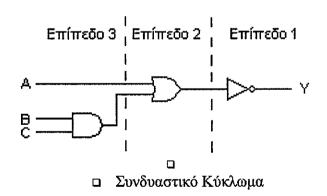

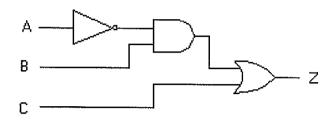

Για τη σχεδίαση του κυκλώματος, ξεκινώντας από την έξοδο προς τις εισόδους του κυκλώματος, σχεδιάζονται οι πύλες του κυκλώματος λαμβάνοντας υπόψη τις λογικές πράξεις της συνάρτησης εξόδου του ΣΚ. Το κύκλωμα χωρίζεται σε επίπεδα που περιέχουν τις πύλες, με βάση την προτεραιότητα των πράξεων. Ξεκινώντας από την έξοδο του ΣΚ προς τις εισόδους του ΣΚ, το κύκλωμα χωρίζεται σε τρία επίπεδα πυλών:

Επίπεδο 1. Μία πύλη ΝΟΤ που χρησιμοποιείται για την εύρεση της εξόδου Υ=(A+BC)' του ΣΚ, αποτελεί το τελευταίο επίπεδο πυλών.

Επίπεδο 2. Μία πύλη OR δύο εισόδων που χρησιμοποιείται για τον υπολογισμό A+BC, αποτελεί το δεύτερο επίπεδο πυλών.

Επίπεδο 3. Μία πύλη ΑΝΟ δύο εισόδων, που χρησιμοποιείται για τον υπολογισμό ΒC, αποτελεί το πρώτο επίπεδο πυλών.

Τα τρία επίπεδα πυλών φαίνονται στο παρακάτω σχήμα, όπου παρουσιάζεται το Συνδυαστικό Κύκλωμα που αναγνωρίζει αν ένας 3-bit αριθμός είναι μικρότερος από 3.

#### ΙΙ. Πλακέτα Εργαστηρίου

1. Ένα συνδυαστικό κύκλωμα (ΣΚ) έχει τρεις εισόδους Α, Β και C και μία έξοδο Υ Y=A'B+AC'

Να κατασκευάσετε τον πίνακα αληθείας του ΣΚ:

| A | В | С | A' | C, | A'B | AC' | Y |

|---|---|---|----|----|-----|-----|---|

| 0 | 0 | 0 |    |    |     |     |   |

| 0 | 0 | 1 |    |    |     |     |   |

| 0 | 1 | 0 |    |    |     |     |   |

| 0 | 1 | 1 |    |    |     |     |   |

| 1 | 0 | 0 |    |    |     |     |   |

| 1 | 0 | 1 |    |    |     |     |   |

| 1 | 1 | 0 |    |    |     |     |   |

| 1 | 1 | 1 |    |    |     |     |   |

Να γράψετε τη συνάρτηση εξόδου Υ του κυκλώματος ως άθροισμα ελαχίστων όρων των μεταβλητών εισόδου Α, Β και C.

Να γράψετε την απλοποιημένη συνάρτηση εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας το ελάχιστο δυνατό πλήθος πυλών ΝΟΤ και πυλών ΑΝD και ΟR δύο εισόδων.

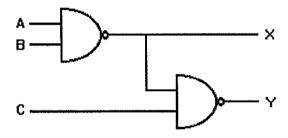

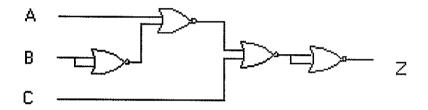

2. Να υλοποιήσετε το παρακάτω συνδυαστικό κύκλωμα:

Να γράψετε τις συναρτήσεις εξόδου Χ και Υ συναρτήσει των εισόδων Α, Β και C. Να συμπληρώσετε τον πίνακα αληθείας:

| A | В | C | X | Y |

|---|---|---|---|---|

| 0 | 0 | 0 |   |   |

| 0 | 0 | 1 |   |   |

| 0 | 1 | 0 |   |   |

| 0 | 1 | 1 |   |   |

| 1 | 0 | 0 |   |   |

| 1 | 0 | 1 |   |   |

| 1 | 1 | 0 |   |   |

| 1 | 1 | 1 |   |   |

3. Ένα συνδυαστικό κύκλωμα χρησιμοποιείται για την ενεργοποίηση ενός συναγερμού σε ένα εργοστάσιο. Το κύκλωμα έχει τρεις εισόδους A, B και C, που συνδέονται με τρεις διακόπτες οι οποίοι είναι συνδεδεμένοι με τρεις αισθητήρες (sensors) SA, SB και SC που ελέγχουν αντίστοιχα την πίεση, την θερμοκρασία και την στάθμη ενός υγρού μέσα σε μία δεξαμενή. Ο αισθητήρας SA δίνει "1" όταν η πίεση υπερβεί κάποιο προκαθορισμένο όριο. Ο αισθητήρας SB δίνει "1" όταν η θερμοκρασία υπερβεί κάποιο προκαθορισμένο όριο. Ο αισθητήρας SC δίνει "0" όταν η στάθμη πέσει κάτω από κάποιο προκαθορισμένο όριο.

Το κύκλωμα έχει μία έξοδο Υ που δίνει "1" για να ενεργοποιηθεί ο συναγερμός όταν η στάθμη πέσει κάτω από το προκαθορισμένο όριο και ταυτόχρονα η πίεση είτε η θερμοκρασία υπερβούν τα προκαθορισμένα όρια.

Να κατασκευάσετε τον πίνακα αληθείας του προβλήματος.

| Α | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

Να γράψετε τη συνάρτηση εξόδου Υ του κυκλώματος ως άθροισμα ελαχίστων όρων των μεταβλητών εισόδου Α, Β και C.

Να γράψετε την απλοποιημένη συνάρτηση εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας το ελάχιστο δυνατό πλήθος πυλών ΝΟΤ και πυλών ΑΝD και ΟR δύο εισόδων.

4. Δίνονται οι συναρτήσεις εξόδου X, Y και Z συναρτήσει των μεταβλητών εισόδου A, B και C σε ένα συνδυαστικό κύκλωμα:

X=(AB)'

Y=(BC)'

Z=B(A+C)

Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα.

| A | В | С | X | Y | Z |

|---|---|---|---|---|---|

| 0 | 0 | 0 |   |   |   |

| 0 | 0 | 1 |   |   |   |

| 0 | 1 | 0 |   |   |   |

| 0 | 1 | 1 |   |   |   |

| 1 | 0 | 0 |   |   |   |

| 1 | 0 | 1 |   |   |   |

| 1 | 1 | 0 |   |   |   |

| 1 | 1 | 1 |   |   |   |

5. Ένα συνδυαστικό κλύκλωμα αναγνωρίζει εκείνα τα δεκαδικά ψηφία από τα δεκαδικά ψηφία 0-15 που διαιρούνται με το 4. Το κύκλωμα θα δέχεται στην είσοδο το δυαδικό ισοδύναμο του δεκαδικού ψηφίου wxyz και θα παράγει στην έξοδο τη συνάρτηση Υ αναγνώρισης των δεκαδικών ψηφίων που διαιρούνται με το 4. Να συμπληρώσετε τον πίνακα αληθείας:

| w | х   | у | Z | Y |

|---|-----|---|---|---|

| 0 | 0   | 0 | 0 |   |

| 0 | 0   | 0 | 1 |   |

| 0 | 0   | 1 | 0 |   |

| 0 | 0   | 1 | 1 |   |

| 0 | 1   | 0 | 0 |   |

| 0 | _ 1 | 0 | 1 |   |

| 0 | 1   | 1 | 0 |   |

| 0 | 1   | 1 | 1 |   |

| 1 | 0   | 0 | 0 |   |

| 1 | 0   | 0 | 1 |   |

| 1 | 0   | 1 | 0 |   |

| 1 | 0   | 1 | 1 |   |

| 1 | 1   | 0 | 0 |   |

| 1 | 1   | 0 | 1 |   |

| 1 | 1   | 1 | 0 |   |

| 1 | 1   | 1 | 1 |   |

Να γράψετε τη συνάρτηση εξόδου Υ συναρτήσει των εισόδων w, x, y και z. Να γράψετε την απλοποιημένη συνάρτηση εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα.

6. Ένα συνδυαστικό κύκλωμα έχει τέσσερεις μεταβλητές εισόδου A, B, C και D και μία έξοδο Y. Το κύκλωμα αποτελείται από τέσσερεις (4) πύλες. Η πρώτη πύλη είναι πύλη ΝΟΤ με είσοδο D και έξοδο D'. Η δεύτερη πύλη είναι πύλη ΑΝD με εισόδους A, B, C και D'. Η τρίτη πύλη είναι πύλη NAND με εισόδους A, B και C. Η τέταρτη πύλη είναι πύλη ΟR με εισόδους τις εξόδους των δύο πυλών ΑΝD και NAND και με έξοδο την έξοδο Y του κυκλώματος.

Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα.

Να συμπληρώσετε τον πίνακα αληθείας.

Να διαπιστώσετε ότι η συνάρτηση εξόδου Υ συναρτήσει των μεταβλητών εισόδου Α, Β, C και D είναι:

Y=(ABCD)'

7. Ένα συνδυαστικό κύκλωμα χρησιμοποιείται για την ενεργοποίηση ενός συναγερμού σε ένα βενζινάδικο. Στο βενζινάδικο υπάρχουν τέσσερις δεξαμενές καυσίμων. Στην δεξαμενή της βενζίνης super υπάρχει ένας αισθητήρας SA που δίνει "1" όταν η στάθμη πέσει κάτω από κάποιο προκαθορισμένο όριο. Στην δεξαμενή της βενζίνης unleaded υπάρχει ένας αισθητήρας SB που δίνει "1" όταν η στάθμη πέσει κάτω από κάποιο προκαθορισμένο όριο. Στην δεξαμενή της βενζίνης super unleaded υπάρχει ένας αισθητήρας SC που δίνει "1" όταν η στάθμη πέσει κάτω από κάποιο προκαθορισμένο όριο. Στην δεξαμενή του πετρελαίου κίνησης υπάρχει ένας αισθητήρας SD που δίνει "0" όταν η θερμοκρασία υπερβεί κάποιο προκαθορισμένο όριο.

Το κύκλωμα έχει τέσσερις εισόδους Α, Β, C και D, που συνδέονται με τέσσερις διακόπτες οι οποίοι είναι συνδεδεμένοι με τους τέσσερις αισθητήρες.

Το κύκλωμα έχει μία έξοδο Υ που δίνει "1" για να ενεργοποιηθεί ο συναγερμός όταν η στάθμη μίας τουλάχιστον από τις δεξαμενές βενζίνης πέσει κάτω από το προκαθορισμένο όριο και ταυτόχρονα η θερμοκρασία της δεξαμενής του πετρελαίου κίνησης υπερβεί το προκαθορισμένο όριο.

Να κατασκευάσετε τον πίνακα αληθείας του προβλήματος.

| A | В | С | D | Y |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 |   |

| 0 | 0 | 0 | 1 |   |

| 0 | 0 | 1 | 0 |   |

| 0 | 0 | 1 | 1 |   |

| 0 | 1 | 0 | 0 |   |

| 0 | 1 | 0 | 1 |   |

| 0 | 1 | 1 | 0 |   |

| 0 | 1 | 1 | 1 |   |

| 1 | 0 | 0 | 0 |   |

| 1 | 0 | 0 | 1 |   |

| 1 | 0 | 1 | 0 |   |

| 1 | 0 | 1 | 1 |   |

| 1 | 1 | 0 | 0 |   |

| 1 | 1 | 0 | 1 |   |

| 1 | 1 | 1 | 0 |   |

| 1 | 1 | 1 | 1 |   |

Να γράψετε τη συνάρτηση εξόδου Υ του κυκλώματος ως άθροισμα ελαχίστων όρων των μεταβλητών εισόδου Α, Β και C.

Να γράψετε την απλοποιημένη συνάρτηση εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας το ελάχιστο δυνατό πλήθος πυλών ΝΟΤ, ΑΝD και ΟR.

## ΙΙΙ. Ολοκληρωμένα Κυκλώματα

1. Ένα συνδυαστικό κύκλωμα (ΣΚ) έχει τρεις εισόδους A, B και C και μία έξοδο Y Y=A'B'+A'B+AB'C'

Να κατασκευάσετε τον πίνακα αληθείας του ΣΚ:

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

Να γράψετε τη συνάρτηση εξόδου Υ του κυκλώματος ως άθροισμα ελαχίστων όρων των μεταβλητών εισόδου Α, Β και C.

Να γράψετε την απλοποιημένη συνάρτηση εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα κατάλληλα ολοκληρωμένα κυκλώματα.

2. Δίνονται οι συναρτήσεις εξόδου X, Y και Z συναρτήσει των μεταβλητών εισόδου A, B και C σε ένα συνδυαστικό κύκλωμα:

X = AB'

Y = (BC)'

Z = A(B+C)

Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα κατάλληλα ολοκληρωμένα κυκλώματα.

Να συμπληρώσετε τον πίνακα αληθείας:

| Α | В | C | X | Y | Z |

|---|---|---|---|---|---|

| 0 | 0 | 0 |   |   |   |

| 0 | 0 | 1 |   |   |   |

| 0 | 1 | 0 |   |   |   |

| 0 | 1 | 1 |   |   |   |

| 1 | 0 | 0 |   |   |   |

| 1 | 0 | 1 |   |   |   |

| 1 | 1 | 0 |   |   |   |

| 1 | 1 | 1 |   |   |   |

3. Ένα συνδυαστικό κύκλωμα χρησιμοποιείται για τον έλεγχο του σηματοδότη μίας διασταύρωσης. Στη διαστάυρωση διασταυρώνεται ένας δρόμος προτεραιότητας με λωρίδες ΛΑ και ΛΒ και ένας δρόμος δευτερεύουσας σημασίας με λωρίδες ΛC και ΛD. Σε κάθε λωρίδα υπάρχει ένας αισθητήρας που ελέγχει την παρουσία αυτοκινήτων δίνοντας "1" όταν υπάρχει τουλάχιστον ένα αυτοκίνητο. Στην διασταύρωση υπάρχει ένας σηματοδότης με δύο φώτα: το ΦΑΒ για τις λωρίδες ΛΑ και ΛΒ και το ΦCD για τις λωρίδες ΛC και ΛD. Το κάθε φως είναι δύο χρωμάτων (κόκκινο και πράσινο). Ο σηματοδότης ελέγχει την κυκλοφορία των αυτοκινήτων σύμφωνα με την ακόλουθη λογική:

Το ΦCD είναι πράσινο όταν

- οι λωρίδες  $\Lambda\dot{C}$  και  $\Lambda D$  είναι κατειλημμένες και τουλάχιστον μία από τις λωρίδες  $\Lambda A$  και  $\Lambda B$  είναι ελεύθερη

- η λωρίδα ΛC ή η λωρίδα ΛD είναι κατειλημμένη και οι λωρίδες ΛΑ και ΛΒ είναι ελεύθερες

Σε όλες τις άλλες περιπτώσεις το ΦCD είναι κόκκινο.

Το ΦΑΒ λειτουργεί εντελώς αντίθετα από το ΦCD.

Το κύκλωμα έχει τέσσερις εισόδους Α, Β, C και D που συνδέονται με τους τέσσερις αισθητήρες.

Το κύκλωμα έχει δύο εξόδους ΥΑΒ και ΥCD που συνδέονται με τα φώτα του σηματοδότη και δίνουν "1" όταν το αντίστοιχο φως είναι πράσινο.

Να κατασκευάσετε τον Πίνακα αληθείας του προβλήματος.

| A | В | С | D | YAB | YCD |

|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 |     |     |

| 0 | 0 | 0 | 1 |     |     |

| 0 | 0 | 1 | 0 |     |     |

| 0 | 0 | 1 | 1 |     |     |

| 0 | 1 | 0 | 0 |     |     |

| 0 | 1 | 0 | 1 |     |     |

| 0 | 1 | 1 | 0 |     |     |

| 0 | 1 | 1 | 1 |     |     |

| 1 | 0 | 0 | 0 |     |     |

| 1 | 0 | 0 | 1 |     |     |

| 1 | 0 | 1 | 0 |     |     |

| 1 | 0 | 1 | 1 |     |     |

| 1 | 1 | 0 | 0 |     |     |

| 1 | 1 | 0 | 1 |     |     |

| 1 | 1 | 1 | 0 |     |     |

| 1 | 1 | 1 | 1 |     |     |

Να γράψετε τις συναρτήσεις εξόδου ΥΑΒ και ΥCD του κυκλώματος ως άθροισμα ελαχίστων όρων των μεταβλητών εισόδου Α, Β, C και D. Να διαπιστώσετε ότι η μία συνάρτηση είναι το συμπλήρωμα της άλλης.

Να γράψετε την απλοποιημένη συνάρτηση εξόδου ΥΑΒ (να χρησιμοποιήσετε χάρτη Karnaugh).

Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα κατάλληλα ολοκληρωμένα κυκλώματα.

# ΙΥ. Πακέτο Λογισμικού

1. Ένα συνδυαστικό κύκλωμα (ΣΚ) έχει τρεις εισόδους Α, Β και C και μία έξοδο Υ Y=A+B'C

Να κατασκευάσετε τον πίνακα αληθείας του ΣΚ:

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

Να γράψετε τη συνάρτηση εξόδου Y του κυκλώματος ως άθροισμα ελαχίστων όρων των μεταβλητών εισόδου A, B και C.

Να γράψετε την απλοποιημένη συνάρτηση εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε το κύκλωμα χρησιμοποιώντας το ελάχιστο δυνατό πλήθος πυλών ΝΟΤ και πυλών ΑΝD και ΟR δύο εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

2. Η κωδικοποίηση  $k\to 2k+1$  μπορεί να υλοποιηθεί με ένα συνδυαστικό κλύκλωμα, το οποίο θα δέχεται στην είσοδο το δυαδικό ισοδύναμο του δεκαδικού ψηφίου k και θα παράγει στην έξοδο το δυαδικό ισοδύναμο του δεκαδικού ψηφίου 2k+1, όπου  $k\in[0,3]$ .

Το συνδυαστικό κύκλωμα έχει δύο εισόδους x και y γιατί  $k \in [0,3]$ .

Το συνδυαστικό κύκλωμα έχει τρεις εξόδους A, B και C γιατί  $2k+1 \in [0,7]$ .

Να κατασκευάσετε τον πίνακα αληθείας του ΣΚ:

| x | у | A | В | С |

|---|---|---|---|---|

| 0 | 0 |   |   |   |

| 0 | 1 |   |   |   |

| 1 | 0 |   |   |   |

| 1 | 1 |   |   |   |

Να γράψετε τις συναρτήσεις εξόδου Α, Β και C συναρτήσει των εισόδων x και y. Να γράψετε τις απλοποιημένες συναρτήσεις εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε το κύκλωμα χρησιμοποιώντας το ελάχιστο δυνατό πλήθος πυλών ΝΟΤ και πυλών ΑΝD και OR δύο εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδων-εξόδων.

3. Ένα συνδυαστικό κύκλωμα χρησιμοποιείται για την αίχνευση λάθους στη λειτουργία ενός σηματοδότη που έχει τρία φώτα: ΦΑ για το κόκκινο, ΦΒ για το πορτοκαλί και ΦC για το πράσινο. Ο σηματοδότης λειτουργεί κανονικά όταν ανάβει μόνον ένα φως. Το κύκλωμα έχει τρεις εισόδους Α, Β και C που συνδέονται με τρεις αισθητήρες SA, SB και SC που δίνουν "1" όταν το αντίστοιχο φως είναι αναμμένο και "0" όταν είναι σβηστό. Το κύκλωμα έχει μία έξοδο Υ που δίνει "1" όταν υπάρχει πρόβλημα στη λειτουργία του σηματοδότη. Να κατασκευάσετε τον πίνακα αληθείας του ΣΚ:

| A | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

Να γράψετε τη συνάρτηση εξόδου Y του κυκλώματος ως άθροισμα ελαχίστων όρων των μεταβλητών εισόδου A, B και C.

Να γράψετε την απλοποιημένη συνάρτηση εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε το κύκλωμα χρησιμοποιώντας το ελάχιστο δυνατό πλήθος πυλών ΝΟΤ και πυλών ΑΝD και ΟR δύο εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

4. Η κωδικοποίηση  $k \rightarrow k^2$  μπορεί να υλοποιηθεί με ένα συνδυαστικό κλύκλωμα, το οποίο θα δέχεται στην είσοδο το δυαδικό ισοδύναμο του δεκαδικού ψηφίου k και θα παράγει στην έξοδο το δυαδικό ισοδύναμο του δεκαδικού ψηφίου  $k^2$  όπου  $k \in [0,7]$ .

Το συνδυαστικό κύκλωμα έχει δύο εισόδους x, y και z γιατί  $k \in [0,7]$ .

Το συνδυαστικό κύκλωμα έχει έξι εξόδους A, B, C, D, E και F γιατί  $k^2 \in [0,49]$ .

Να κατασκευάσετε τον πίνακα αληθείας του ΣΚ:

| Х | у       | Z | A | В | C | D | Е | F                                     |

|---|---------|---|---|---|---|---|---|---------------------------------------|

|   |         |   |   |   |   |   |   |                                       |

|   |         |   |   |   |   |   |   | · · · · · · · · · · · · · · · · · · · |

|   |         |   |   |   |   |   |   |                                       |

|   |         |   |   |   |   |   |   |                                       |

|   |         |   |   |   |   |   |   |                                       |

|   |         |   |   |   |   |   |   |                                       |

|   | <u></u> |   |   |   |   |   |   |                                       |

Να γράψετε τις απλοποιημένες συναρτήσεις εξόδου (να χρησιμοποιήσετε χάρτη Karnaugh). Να σχεδιάσετε το κύκλωμα χρησιμοποιώντας το ελάχιστο δυνατό πλήθος πυλών ΝΟΤ και πυλών ΑΝD και ΟR δύο εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδων-εξόδων.

## ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 8 ΟΙΚΟΥΜΕΝΙΚΈΣ ΠΎΛΕΣ ΔΥΟ ΕΙΣΟΔΩΝ

## Ι. Βασική Θεωρία

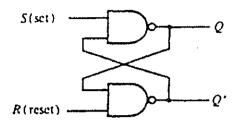

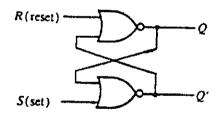

Οι πύλες NAND και NOR δύο εισόδων ονομάζονται οικουμενικές πύλες (universal gates) γιατί κάθε συνδυαστικό κύκλωμα μπορεί να υλοποιηθεί μόνο με πύλες NAND δύο εισόδων ή μόνο με πύλες NOR δύο εισόδων.

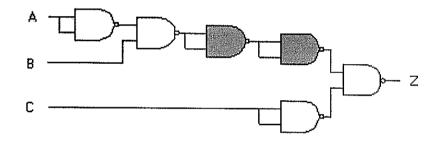

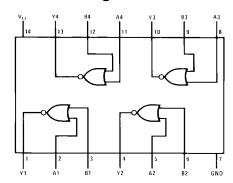

Κάθε πύλη NOT και AND και OR δύο εισόδων μπορεί να αντικατασταθεί από ένα ισοδύναμο κύκλωμα με αποκλειστική χρησιμοποίηση είτε πυλών NAND είτε πυλών NOR δύο εισόδων. Στο παρακάτω σχήμα βλέπουμε τα κυκλώματα που είναι ισοδύναμα με τις βασικές πύλες NOT, AND και OR, χρησιμοποιώντας μόνο πύλες NAND δύο εισόδων.

Υλοποίηση πυλών ΝΟΤ, ΑΝΟ και ΟR με πύλες ΝΑΝΟ δύο εισόδων

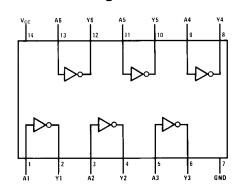

Στο παρακάτω σχήμα βλέπουμε τα κυκλώματα που είναι ισοδύναμα με τις βασικές πύλες NOT, AND και OR, χρησιμοποιώντας μόνο πύλες NOR δύο εισόδων.

Υλοποίηση πυλών ΝΟΤ, ΑΝΟ και ΟR με πύλες ΝΟR δύο εισόδων

Ετσι, αν θέλουμε να σχεδιάσουμε και να κατασκευάσουμε ένα κύκλωμα με οικουμενικές πύλες NAND ή NOR δύο εισόδων, μπορούμε να το σχεδιάσουμε πρώτα με πύλες NOT, AND και OR και στη συνέχεια να αντικαταστήσουμε την κάθε πύλη με το ισοδύναμο κύκλωμα. Αν στο κύκλωμα υπάρχουν δύο διαδοχικές πύλες NAND ή NOR που αντιστοιχούν σε πύλες NOT, τότε οι δύο διαδοχικές πύλες διαγράφονται και το κύκλωμα απλοποιείται.

### Παράδειγμα 1.

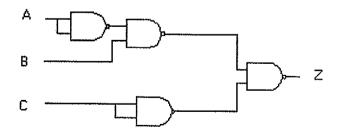

Θέλουμε να σχεδιάσουμε με οικουμενικές πύλες ΝΑΝΟ δύο εισόδων το συνδυαστικό κύκλωμα που υλοποιεί τη λογική συνάρτηση:

#### Z=A'B+C

Σχεδιάζουμε στην αρχή το κύκλωμα με πύλες NOT, AND και OR:

Κύκλωμα της συνάρτησης Ζ=Α'Β+С με πύλες ΝΟΤ, ΑΝΟ και ΟR

Στη συνέχεια αντικαθιστούμε την κάθε πύλη με το ισοδύναμο κύκλωμα με πύλες ΝΑΝΟ δύο εισόδων:

Κύκλωμα της συνάρτησης Ζ=Α'Β+С με πύλες NAND δύο εισόδων

Στο κύκλωμα αυτό παρατηρούμε ότι υπάρχουν διαδοχικές πύλες NAND δύο εισόδων που αντιστοιχούν σε πύλες ΝΟΤ. Αυτές οι δύο διαδοχικές πύλες διαγράφονται και το κύκλωμα απλοποιείται:

Απλοποιημένο Κύκλωμα της συνάρτησης Ζ=Α'Β+С με πύλες ΝΑΝΟ δύο εισόδων

Ένας άλλος τρόπος είναι να επεξεργαστούμε τη λογική συνάρτηση.

Προφανώς ισχύει ότι:

Z=(Z')'

Επομένως, η συνάρτηση γράφεται:

Z=(A'B+C)=((A'B+C)')'

Σύμφωνα με το θεώρημα De Morgan η συνάρτηση γίνεται:

Z=((A'B)'C')'

Η συνάρτηση αυτή υλοποιείται αποκλειστικά με πύλες NAND δύο εισόδων, όπως ακριβώς έγινε προηγουμένως.

Αν προχωρήσουμε την επεξεργασία της εξίσωσης χρησιμοποιώντας το θεώρημα De Morgan έχουμε:

Z=A'B+C=((A'B)'C')'=((A+B')C')'=(A+B')+C=(((A+B')+C)')'

Η συνάρτηση αυτή υλοποιείται αποκλειστικά με πύλες NOR δύο εισόδων:

Κύκλωμα της συνάρτησης Ζ=Α'+C με πύλες NOR δύο εισόδων

#### Η. Πλακέτα Εργαστηρίου

- 1. Να υλοποιήσετε μία πύλη ΝΟΤ χρησιμοποιώντας μία πύλη NAND με βραχυκυκλωμένες τις εισόδους.

- 2. Να υλοποιήσετε μία πύλη ΑΝΟ δύο εισόδων χρησιμοποιώντας δύο πύλες NAND.

- 3. Να υλοποιήσετε μία πύλη ΟΚ δύο εισόδων χρησιμοποιώντας τρεις πύλες NAND.

- 4. Ένα συνδυαστικό κύκλωμα έχει τρεις εισόδους x, y και z και μία έξοδο F,  $\eta$  οποία δίνεται ως άθροισμα ελαχίστων όρων:

$F(x,y,z)=\Sigma(0,2,4,6,7)$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες NAND δύο εισόδων.

- 5. Να υλοποιήσετε μία πύλη NOT χρησιμοποιώντας μία πύλη NOR δύο εισόδων με βραχυκυκλωμένες τις εισόδους.

- 6. Να υλοποιήσετε μία πύλη AND δύο εισόδων χρησιμοποιώντας τρεις πύλες NOR.

- 7. Να υλοποιήσετε μία πύλη OR δύο εισόδων χρησιμοποιώντας δύο πύλες NOR.

- 8. Ένα συνδυαστικό κύκλωμα έχει τρεις εισόδους x, y και z και μία έξοδο F, η οποία δίνεται ως άθροισμα ελαχίστων όρων:

$F(x,y,z)=\Sigma(2,4,6)$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες NOR δύο εισόδων.

# ΙΙΙ. Ολοκληρωμένα Κυκλώματα

- 1. Να υλοποιήσετε μία πύλη ΝΟΤ χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7400.

- 2. Να υλοποιήσετε μία πύλη ΑΝΟ δύο εισόδων χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7400.

- 3. Να υλοποιήσετε μία πύλη OR δύο εισόδων χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7400.

- 4. Να υλοποιήσετε μία πύλη ΝΟΤ χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7402.

- 5. Να υλοποιήσετε μία πύλη AND δύο εισόδων χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7402.

- 6. Να υλοποιήσετε μία πύλη OR δύο εισόδων χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7402.

- 7. Ένα συνδυαστικό κύκλωμα έχει τρεις εισόδους A, B και C και μία έξοδο F με συνάρτηση: F(A,B,C)=AB'+A'B+AB'C'

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να σχεδιάσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες NAND δύο εισόδων.

Να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα κατάλληλα ολοκληρωμένα κυκλώματα.

### ΙΥ. Πακέτο Λογισμικού

1. Να σχεδιάσετε μία πύλη NOT χρησιμοποιώντας μία πύλη NAND δύο εισόδων με βραχυκυκλωμένες τις εισόδους.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

2. Να υλοποιήσετε μία πύλη AND δύο εισόδων χρησιμοποιώντας δύο πύλες NAND δύο εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

3. Να υλοποιήσετε μία πύλη OR δύο εισόδων χρησιμοποιώντας τρεις πύλες NAND δύο εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

4. Να σχεδιάσετε μία πύλη NOT χρησιμοποιώντας μία πύλη NOR δύο εισόδων με βραχυκυκλωμένες τις εισόδους.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

**5. Να υλοποιήσετε μία πύλη ΑΝΟ δύο εισόδων χρησιμοποιώντ**ας δύο πύλες ΝΟR δύο **εισόδων.**

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

6. Να υλοποιήσετε μία πύλη OR δύο εισόδων χρησιμοποιώντας τρεις πύλες NOR δύο εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

7. Ένα συνδυαστικό κύκλωμα έχει τρεις εισόδους Α, Β και C και μία έξοδο F με συνάρτηση: F(A,B,C)=AB'+A'B+A'BC'

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να σχεδιάσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες NOR δύο εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

#### ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 9 ΟΙΚΟΥΜΕΝΙΚΈΣ ΠΥΛΈΣ ΠΟΛΛΑΠΛΩΝ ΕΙΣΟΔΩΝ

#### Ι. Βασική Θεωρία

Οι πύλες NAND και NOR ονομάζονται οικουμενικές πύλες (universal gates) γιατί κάθε συνδυαστικό κύκλωμα μπορεί να υλοποιηθεί μόνο με πύλες NAND ή μόνο με πύλες NOR πολλαπλών εισόδων.

Κάθε συνδυαστικό κύκλωμα μπορεί να υλοποιηθεί μόνο με πύλες NAND ή μόνο με πύλες NOR πολλαπλών εισόδων σε δύο επίπεδα. Η μέθοδος σχεδίασης συνδυαστικού κυκλώματος μόνο με πύλες NAND ή NOR πολλαπλών εισόδων σε δύο επίπεδα είναι η ακόλουθη:

- έκφραση των συναρτήσεων εξόδου του συνδυαστικού κυκλώματος

- ως αθροίσματα γινομένων, όταν απαιτείται υλοποίηση με πύλες NAND

- ως γινόμενα αθροισμάτων, όταν απαιτείται υλοποίηση με πύλες NOR όπου ισχύει η υπόθεση ότι οι είσοδοι είναι διαθέσιμοι τόσο στην κανονική όσο και στη συμπληρωματική τους μορφή

- πύλες πρώτου επιπέδου

- σε κάθε γινόμενο αντιστοιχεί μία πύλη NAND με εισόδους τους παράγοντες του γινομένου, όταν απαιτείται υλοποίηση με πύλες NAND

- σε κάθε άθροισμα αντιστοιχεί μία πύλη NOR με εισόδους τους όρους του αθροίσματος, όταν απαιτείται υλοποίηση με πύλες NOR

- πύλη δεύτερου επιπέδου μία πύλη με εισόδους που τροφοδοτούνται από τις εξόδους των πυλών του πρώτου επιπέδου

- διαγραφή κάθε πύλης του πρώτου επιπέδου που τροφοδοτείται από μία είσοδο και αντικατάσταση της εισόδου με το συμπλήρωμά της, με το οποίο τροφοδοτείται η πύλη του δεύτερου επιπέδου (ισχύει η υπόθεση ότι οι είσοδοι είναι διαθέσιμοι τόσο στην κανονική όσο και στη συμπληρωματική τους μορφή)

## ΙΙ. Πλακέτα Εργαστηρίου

1. Ένα συνδυαστικό κύκλωμα έχει τρεις εισόδους x, y και z και μία έξοδο F,  $\eta$  οποία δίνεται ως άθροισμα ελαχίστων όρων:

$F(x,y,z)=\Sigma(0,7)$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες ΝΑΝD πολλαπλών εισόδων.

2. Ένα συνδυαστικό κύκλωμα έχει τρεις εισόδους x,y και z και μία έξοδο  $F,\eta$  οποία δίνεται ως άθροισμα ελαχίστων όρων:

$F(x,y,z)=\Sigma(0,6)$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να υλοποιήσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες ΝΟR πολλαπλών εισόδων.

## ΙΙΙ. Ολοκληρωμένα Κυκλώματα

1. Ένα συνδυαστικό κύκλωμα έχει τρεις εισόδους x, y και z και μία έξοδο F,  $\eta$  οποία δίνεται ως άθροισμα ελαχίστων όρων:

$F(x,y,z)=\Sigma(0,3,5,6,7)$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να σχεδιάσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες ΝΑΝΟ πολλαπλών εισόδων.

Να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα κατάλληλα ολοκληρωμένα κυκλώματα.

2. Ένα συνδυαστικό κύκλωμα έχει τρεις εισόδους x, y και z και μία έξοδο F,  $\eta$  οποία δίνεται ως γινόμενο μεγίστων όρων:

$F(x,y,z)=\Pi(1,2,3,4,7)$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να απλοποιήσετε τη λογική συνάρτηση και να σχεδιάσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες NOR πολλαπλών εισόδων.

Να υλοποιήσετε το κύκλωμα χρησιμοποιώντας τα κατάλληλα ολοκληρωμένα κυκλώματα.

#### ΙΥ. Πακέτο Λογισμικού

1. Ένα συνδυαστικό κύκλωμα έχει τέσσερις εισόδους A, B, C και D και μία έξοδο F με συνάρτηση:

F(A,B,C,D)=AB'C+A'BD+BC'D'

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να σχεδιάσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες ΝΑΝΟ πολλαπλών εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

2. Ένα συνδυαστικό κύκλωμα έχει τέσσερις εισόδους A, B, C και D και μία έξοδο F με συνάρτηση:

$$F(A,B,C,D)=(A+B'+C)(B'+C'+D)(A'+D')$$

Να κατασκευάσετε το χάρτη Karnaugh της συνάρτησης.

Να σχεδιάσετε το κύκλωμα χρησιμοποιώντας μόνο πύλες NOR πολλαπλών εισόδων.

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

# ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 10 ΔΥΑΔΙΚΉ ΠΡΟΣΘΈΣΗ ΚΑΙ ΑΦΑΙΡΕΣΉ

#### Ι. Βασική Θεωρία

Δυαδική Πρόσθεση

Ημιαθροιστής

Το κύκλωμα που πραγματοποιεί την πρόσθεση των δύο ψηφίων χωρίς να λαμβάνει υπόψη τυχόν προηγούμενο κρατούμενο ονομάζεται Ημιαθροιστής. Ο Ημιαθροιστής έχει δύο εισόδους κ και y (τα bit που προστίθενται) και δύο εξόδους C (κρατούμενο) και S (άθροισμα). Ο πίνακας αληθείας του Ημιαθροιστή είναι:

| Х | у | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Οι εξισώσεις του Ημιαθροιστή είναι: S=x'y+xy'=x\Py C=xy

Πλήρης Αθροιστή

Το κύκλωμα που πραγματοποιεί την πρόσθεση των δύο ψηφίων λαμβάνοντας υπόψη τυχόν προηγούμενο κρατούμενο ονομάζεται Πλήρης Αθροιστής. Ο Πλήρης Αθροιστής έχει τρεις εισόδους x, y (τα bit που προστίθενται) και z (κρατούμενο εισόδου) και δύο εξόδους C (κρατούμενο εξόδου) και S (άθροισμα).

Ο πίνακας αληθείας του Πλήρη Αθροιστή είναι:

| X | у | Z | C | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Οι εξισώσεις του Πλήρη Αθροιστή είναι:

$S=(x \oplus y) \oplus z$

$C=xy+(x\oplus y)z$

Ενας Πλήρης Αθροιστής μπορεί να υλοποιηθεί με δύο Ημιαθροιστές και μία πύλη ΟR.

#### Δυαδική Αφαίρεση

#### Ημιαφαιρέτης

Το κύκλωμα που πραγματοποιεί την αφαίρεση των δύο ψηφίων χωρίς να υπολογίζει τυχόν προηγούμενο δανεικό ονομάζεται Ημιαφαιρέτης. Ο Ημιαφαιρέτης έχει δύο εισόδους x και y (τα bit που αφαιρούνται) και δύο εξόδους B (δανεικό) και D (διαφορά). Ο πίνακας αλήθειας του Ημιαφαιρέτη είναι:

| Х | У | В | D |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 |

Οι εξισώσεις του Ημιαφαιρέτη είναι:

D=x⊕y

B=x'y

## Πλήρης Αφαιρέτης

Το κύκλωμα που πραγματοποιεί την αφαίρεση των δύο ψηφίων λαμβάνοντας υπόψη τυχόν προηγούμενο δανεικό ονομάζεται Πλήρης Αφαιρέτης. Ο Πλήρης Αφαιρέτης έχει τρεις εισόδους x, y (τα bit που προστίθενται) και z (δανεικό εισόδου) και δύο εξόδους B (δανεικό εξόδου) και D (διαφορά).

Ο πίνακας αλήθειας του Πλήρη Αφαιρέτη είναι:

| Х | у | Z | В | D |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Οι εξισώσεις του Πλήρη Αφαιρέτη είναι:

$D=(x\oplus y)\oplus z$

$B=x'y+(x\oplus y)'z$

Ενας Πλήρης Αφαιρέτης μπορεί να υλοποιηθεί με δύο Ημιαφαιρέτες και μία πύλη ΟR.

## ΙΙ. Πλακέτα Εργαστηρίου

- 1. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Ημιαθροιστή.

- 2. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Πλήρη Αθροιστή χρησιμοποιώντας δύο Ημιαθροιστές και μία πύλη ΟR.

- 3. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Ημιαφαιρέτη χρησιμοποιώντας έναν Ημιαθροιστή και πύλες NOT.

- 4. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Πλήρη Αφαιρέτη χρησιμοποιώντας έναν Πλήρη Αθροιστή και πύλες ΝΟΤ.

#### ΙΙΙ. Ολοκληρωμένα Κυκλώματα

- 1. Να υλοποιήσετε έναν παράλληλο δυαδικό αθροιστή 4-bit χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 7483.

- 2. Να εκτελέσετε τις δυαδικές προσθέσεις:

0011+0100

0011+0111

0111+1010

1010+1111

#### ΙΥ. Πακέτο Λογισμικού

- 1. Να σχεδιάσετε έναν παράλληλο δυαδικό αθροιστή/αφαιρέτη 4-bit χρησιμοποιώντας τα ολοκληρωμένα κυκλώματα 7483 και 7486.

- 2. Να εκτελέσετε τις δυαδικές προσθέσεις/αφαιρέσεις:

0011+0111

0111+1010

1100-1001

1001-1100

Να σχεδιάσετε τις κυματομορφές εισόδου και την κυματομορφή εξόδου.

## ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 11 ΑΠΟΚΩΛΙΚΟΠΟΙΉΤΕΣ - ΑΠΟΠΛΕΚΤΈΣ

## Ι. Βασική Θεωρία

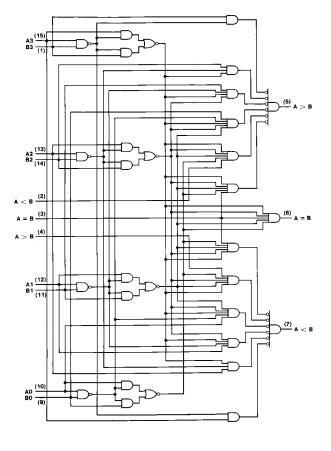

Ο Αποκωδικοποιητής (Decoder)  $nx2^n$  είναι ένα συνδυαστικό κύκλωμα που μετατρέπει την δυδική πληροφορία n γραμμών εισόδου σε  $2^n$  γραμμές εξόδου που αποτελούν τους ελάχιστους όρους των μεταβλητών εισόδου.

Για παράδειγμα, ο Αποκωδικοποιητής 2x4 έχει δύο εισόδους Α και Β και τέσσερις εξόδους D0. D1. D2 και D3.

Ο πίνακας αληθείας του Αποκωδικοποιητή 2x4 είναι:

| A | В | D0 | D1 | D2 | D3 |

|---|---|----|----|----|----|

| 0 | 0 | 1  | 0  | 0  | 0  |

| 0 | 1 | 0  | 1  | 0  | 0  |

| 1 | 0 | 0  | 0  | 1  | 0  |

| 1 | 1 | 0  | 0  | 0  | 1  |

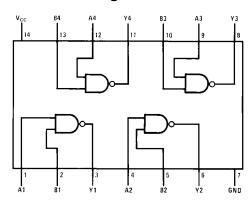

Οι συναρτήσεις εξόδου του Αποκωδικοποιητή 2x4 είναι:

D0=A'B'

D1=A'B

D2=AB'

D3=AB

Ο Αποπλέκτης (Demultiplexer)  $1x2^n$  είναι ένα συνδυαστικό κύκλωμα που δέχεται πληροφορίες από μία γραμμή εισόδου και τις μεταβιβάζει σε μία από τις  $2^n$  γραμμές εξόδου, ανάλογα με τις τιμές των η γραμμών επιλογής.

Ένας Αποκωδικοποιητής με είσοδο επίτρεψης μπορεί να χρησιμοποιηθεί και ως Αποπλέκτης, οπότε ονομάζεται Αποκωδικοποιητής/Αποπλέκτης.

Ο Αποκωδικοποιητής/Αποπλέκτης παράγει στις εξόδους του τα συμπληρώματα των ελάχιστων όρων των μεταβλητών εισόδου, δηλαδή τους μέγιστους όρους των μεταβλητών εισόδου.

Για παράδειγμα, ο Αποκωδικοποιητής/Αποπλέκτης 2x4 έχει δύο εισόδους Α και Β και τέσσερις εξόδους D0, D1, D2 και D3.

Ο πίνακας αληθείας του Αποκωδικοποιητή/Αποπλέκτη 2x4 είναι:

| A | В | D0' | D1' | D2' | D3' |

|---|---|-----|-----|-----|-----|

| 0 | 0 | 0   | 1   | 1   | 1   |

| 0 | 1 | 1   | 0   | 1   | 1   |

| 1 | 0 | 1   | 1   | 0   | 1   |

| 1 | 1 | 1   | 1   | 1   | 0   |

Οι συναρτήσεις εξόδου του Αποκωδικοποιητή/Αποπλέκτη 2x4 είναι:

D0=A+B

D1=A+B'

D2=A'+B

D3=A'+B'

Κάθε λογική συνάρτηση η μεταβλητών μπορεί να υλοποιηθεί με έναν **Αποκωδικοποιητή**  $nx2^n$  και μία πύλη **OR**.

Η διαδικασία που ακολουθείται είναι η εξής:

- γράφεται η λογική συνάρτηση σε μορφή αθροίσματος ελαχίστων όρων

- σχεδιάζουμε το κύκλωμα με έναν Αποκωδικοποιητή nx2<sup>n</sup> και μία πύλη OR με εισόδους τους ελάχιστους όρους που αντιστοιχούν σε "1".

Κάθε συνδυαστικό κύκλωμα η εισόδων και m εξόδων μπορεί να υλοποιηθεί με έναν Αποκωδικοποιητή  $mx^n$  και m πύλες OR.

Κάθε λογική συνάρτηση η μεταβλητών μπορεί να υλοποιηθεί με έναν  $\mathbf{A}$ ποκωδικοποιητή/ $\mathbf{A}$ ποπλέκτη  $\mathbf{n}$ χ $\mathbf{n}$  και μία πύλη  $\mathbf{N}$

Κάθε συνδυαστικό κύκλωμα η εισόδων και η εξόδων μπορεί να υλοποιηθεί με έναν Αποκωδικοποιητή/Αποπλέκτη ηχ2<sup>n</sup> και η πύλες NAND.

## ΙΙ. Πλακέτα Εργαστηρίου

- 1. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Αποκωδικοποιητή 2x4. Να χρησιμοποιήσετε τον Αποκωδικοποιητή 2x4 και δύο πύλες OR για να υλοποιήσετε ένα συνδυαστικό κύκλωμα δύο εισόδων A και B και δύο εξόδων  $F1(A,B)=\Sigma(0,1,3)$  και  $F2(A,B)=\Sigma(0,2)$ .

- 2. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Αποκωδικοποιητή/Αποπλέκτη 2x4. Να χρησιμοποιήσετε τον Αποκωδικοποιητή/Αποπλέκτη και δύο πύλες NAND για να υλοποιήσετε ένα συνδυαστικό κύκλωμα δύο εισόδων Α και Β και δύο εξόδων F1(A,B)=Σ(0,3) και F2(A,B)=Σ(1,2,3).

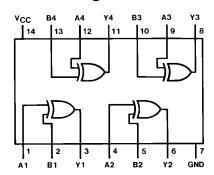

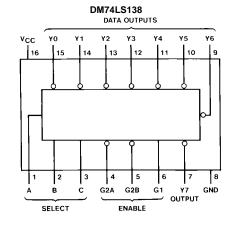

#### ΙΙΙ. Ολοκληρωμένα Κυκλώματα

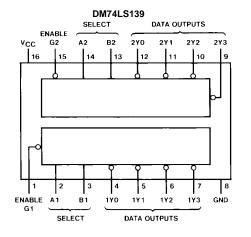

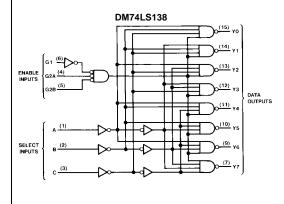

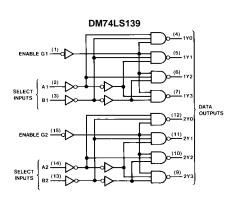

- 1. Να υλοποιήσετε έναν Αποκωδικοποιητή/Αποπλέκτη 3x8 χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 74138.

- 2. Να χρησιμοποιήσετε το ολοκληρωμένα κυκλώματα 74138 και 7420 για να υλοποιήσετε τη συνάρτηση  $F(A,B,C)=\Sigma(0,5,6,7)$

#### ΙΥ. Πακέτο Λογισμικού

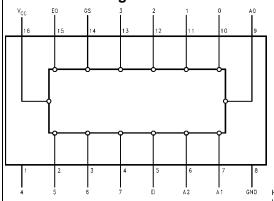

- 1. Να σχεδιάσετε έναν Αποκωδικοποιητή/Αποπλέκτη 4x16 χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 74154. Να σχεδιάσετε το κύκλωμα και τις κυματομορφές εισόδων-εξόδων.

- 2. Να χρησιμοποιήσετε το ολοκληρωμένα κυκλώματα 74138 και 7420 για να υλοποιήσετε τη συνάρτηση  $F(A,B,C,D)=\Sigma(0,1,14,15)$ Να σχεδιάσετε το κύκλωμα και τις κυματομορφές εισόδων-εξόδου.

## ΕΡΓΑΣΤΗΡΙΑΚΗ ΑΣΚΗΣΗ 12 ΚΩΔΙΚΟΠΟΙΗΤΕΣ

## Ι. Βασική Θεωρία

Ο Κωδικοποιητής (Encoder)  $2^n$ χη είναι ένα συνδιαστικό κύκλωμα που έχει είσοδο από  $2^n$  γραμμές και δίνει έξοδο από η γραμμές. Εκτελεί δηλαδή την αντίστροφη εργασία από αυτή του Αποκωδικοποιητή.

Ο Κωδικοποιητής 4x2 παράγει στην έξοδό του τον δυαδικό κώδικα που αντιστοιχεί στις εισόδους του.

Για παράδειγμα, ο Κωδικοποιητής 4x2 έχει τέσσερις εισόδους D0, D1, D2 και D3 και δύο εξόδους x και y.

Ο πίνακας αληθείας του Κωδικοποιητή 4χ2 είναι:

| D0 | D1 | D2 | D3 | X | У |

|----|----|----|----|---|---|

| 1  | 0  | 0  | 0  | 0 | 0 |

| 0  | 1  | 0  | 0  | 0 | 1 |

| 0  | 0  | 1  | 0  | 1 | 0 |

| 0  | 0  | 0  | 1  | 1 | 1 |

Οι συναρτήσεις εξόδου του Κωδικοποιητή 4χ2 είναι:

x=D2+D3

y=D1+D3

Αυτή η σχεδίαση του Κωδικοποιητή παρουσιάζει τα εξής δύο βασικά προβλήματα: Πρόβλημα 1.

Οταν όλες οι είσοδοι ενός Κωδικοποιητή είναι "0", τότε όλες οι έξοδοι του Κωδικοποιητή είναι "0", γεγονός που πρέπει να συμβαίνει μόνον όταν το πλέον σημαντικό bit της εισόδου είναι "1" και όλα τα υπόλοιπα bits της εισόδου είναι "0" (αυτό απαιτεί η σωστή κωδικοποίηση).

Το πρόβλημα αυτό αντιμετωπίζεται με την προσθήκη μίας επιπλέον εξόδου στον Κωδικοποιητή, που ονομάζεται ενδείκτης έγκυρης εξόδου.

Πρόβλημα 2.

Οταν δύο ή περισσότερες είσοδοι ενός Κωδικοποιητή είναι "1", τότε μπορεί να προκύψει σφάλμα στην κωδικοποίηση.

Για παράδειγμα, αν οι είσοδοι του παραπάνω Κωδικοποιητή 4χ2 είναι:

D0=0, D1=1, D2=1 και D3=0

τότε από τις συναρτήσεις εξόδου του Κωδικοποιητή 4χ2 προκύπτει ότι:

x=D2+D3=1

y=D1+D3=1

Οι έξοδοι όμως πρέπει να είναι:

x=1 και y=1

μόνον όταν οι είσοδοι είναι:

D0=0, D1=0, D2=0 και D3=1

(αυτό σημαίνει σωστή κωδικοποίηση)

Το πρόβλημα αυτό αντιμετωπίζεται με τον καθορισμό προτεραιότητας στις εισόδους του Κωδικοποιητή: η είσοδος με την μεγαλύτερη προτεραιότητα καθορίζει την έξοδο.

Ο Κωδικοποιητής προτεραιότητας είναι ένας Κωδικοποιητής όπου αν δύο ή περισσότερες είσοδοί του είναι ταυτόχρονα "1", τότε η είσοδος με την μεγαλύτερη προτεραιότητα καθορίζει την έξοδο του Κωδικοποιητή. Ο Κωδικοποιητής προτεραιότητας έχει μία έξοδο που ελέγγει την εγκυρότητα της εξόδου και ονομάζεται ενδείκτης έγκυρης εξόδου.

Για παράδειγμα, ο Κωδικοποιητής προτεραιότητας 4x2 έχει τέσσερις εισόδους D0, D1, D2 και D3 και τρεις εξόδους x, y και z (ενδείκτης έγκυρης εξόδου). Αν ο Κωδικοποιητής έχει προτεραιότητα από το D3 (μέγιστη προτεραιότητα) προς το D0 (ελάχιστη προτεραιότητα), τότε ο πίνακας αληθείας του Κωδικοποιητή προτεραιότητας είναι:

| D0 | D1 | D2 | D3 | х | у | Z |

|----|----|----|----|---|---|---|

| 0  | 0  | 0  | 0  | X | X | 0 |

| 1  | 0  | 0  | 0  | 0 | 0 | 1 |

| X  | 1  | 0  | 0  | 0 | 1 | 1 |

| X  | X  | 1  | 0  | 1 | 0 | 1 |

| X  | X  | X  | 1  | 1 | 1 | 1 |

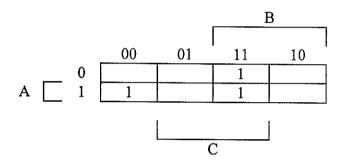

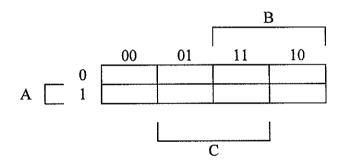

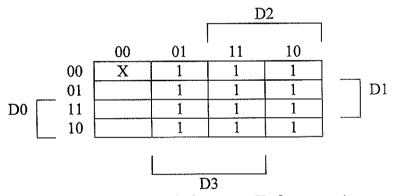

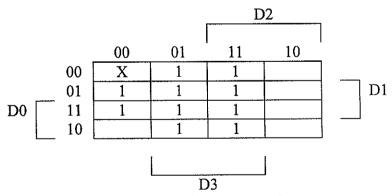

Οι χάρτες Karnaugh των συναρτήσεων εξόδου x και y του Κωδικοποιητή προτεραιότητας είναι:

Χάρτης Karnaugh της συνάρτησης εξόδου x του Κωδικοποιητή προτεραιότητας

Χάρτης Karnaugh της συνάρτησης εξόδου y του Κωδικοποιητή προτεραιότητας

Οι συναρτήσεις εξόδου του Κωδικοποιητή προτεραιότητας είναι:

x=D2+D3

y=D1D2'+D3

z=D0+D1+D2+D3

#### Η. Πλακέτα Εργαστηρίου

- 1. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Κωδικοποιητή 4x2 που έχει τέσσερις εισόδους D0, D1, D2 και D3 και δύο εξόδους x και y.

- 2. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Κωδικοποιητή προτεραιότητας 4x2 που έχει τέσσερις εισόδους D0, D1, D2 και D3 και τρεις εξόδους x, y και z (ενδείκτης έγκυρης εξόδου) με προτεραιότητα από το D3 (μέγιστη προτεραιότητα) προς το D0 (ελάχιστη προτεραιότητα).

# ΙΙΙ. Ολοκληρωμένα Κυκλώματα

1. Να σχεδιάσετε και να υλοποιήσετε το κύκλωμα ενός Κωδικοποιητή 8x3 που έχει οκτώ εισόδους D0, D1, D2, D3, D4, D5, D6 και D7 και τρεις εξόδους x, y και z.

Να παρατηρήσετε ότι:

x=D4+D5+D6+D7

y=D2+D3+D6+D7

z=D1+D3+D5+D7

2. Να υλοποιήσετε έναν Κωδικοποιητή προτεραιότητας 8x3 χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 74148.

Τι προτεραιότητα έχει ο Κωδικοποιητής;

# ΙΥ. Πακέτο Λογισμικού

1. Να σχεδιάσετε έναν Κωδικοποιητή προτεραιότητας 8x3 χρησιμοποιώντας το ολοκληρωμένο κύκλωμα 74148.

Να σχεδιάσετε το κύκλωμα και τις κυματομορφές εισόδων-εξόδων.

2. Ένας Κωδικοποιητής προτεραιότητας 4x2 που έχει τέσσερις εισόδους D0, D1, D2 και D3 και τρεις εξόδους x, y και z (ενδείκτης έγκυρης εξόδου) έχει τον παρακάτω πίνακα αληθείας:

| D0 | D1 | D2 | D3 | X | У | Z |

|----|----|----|----|---|---|---|

| 0  | 0  | 0  | 0  | X | X | 0 |

| 1  | X  | X  | X  | 0 | 0 | 1 |

| 0  | 1  | X  | X  | 0 | 1 | 1 |

| 0  | 0  | 1  | X  | 1 | 0 | 1 |

| 0  | 0  | 0  | 1  | 1 | 1 | 1 |

Να εκφράσετε τις εξόδους του Κωδικοποιητή x, y και z (ενδείκτης έγκυρης εξόδου) συναρτήσει των εισόδων του D0, D1, D2 και D3.

Να σχεδιάσετε το κύκλωμα και τις κυματομορφές εισόδων-εξόδων.

Τι προτεραιότητα έγει ο Κωδικοποιητής;

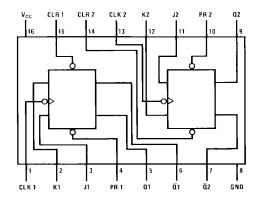

## ΕΡΓΑΣΤΗΡΙΑΚΉ ΑΣΚΉΣΗ 13 ΠΟΛΥΠΛΕΚΤΈΣ

# Ι. Βασική Θεωρία

Ο **Πολυπλέκτης** (Multiplexer)  $2^n$ x1 είναι ένα συνδυαστικό κύκλωμα που επιλέγει δυαδικές πληροφορίες ανάμεσα σε  $2^n$  γραμμές εισόδου ανάλογα με τις τιμές των n γραμμών επιλογής και τις κατευθύνει σε 1 γραμμή εξόδου.

## Παράδειγμα.

Ο Πολυπλέκτης 2x1 έχει δύο εισόδους Ι0 και Ι1, μία επιλογή S και μία έξοδο Υ.

Ο πίνακας λειτουργίας του Πολυπλέκτη 2x1 είναι:

| S | Y  |

|---|----|

| 0 | I0 |

| 1 | I1 |

Ο πίνακας αληθείας του Πολυπλέκτη 2x1 είναι:

| S | I1 | 10 | Y |

|---|----|----|---|

| 0 | 0  | 0  | 0 |

| 0 | 0  | 1  | 1 |

| 0 | 1  | 0  | 0 |

| 0 | 1  | 1  | 1 |

| 1 | 0  | 0  | 0 |

| 1 | 0  | 1  | 0 |

| 1 | 1  | 0  | 1 |

| 1 | 1  | 1  | 1 |

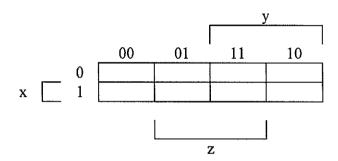

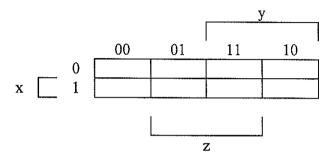

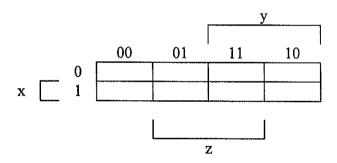

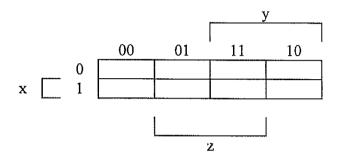

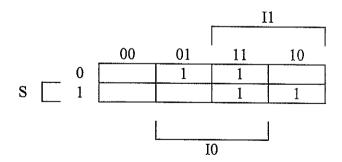

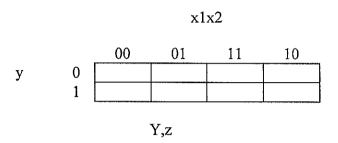

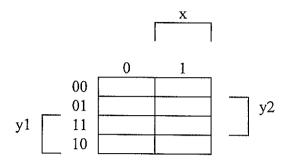

Ο χάρτης Karnaugh της συνάρτησης εξόδου του Πολυπλέκτη 2x1 είναι:

Η συνάρτηση εξόδου του Πολυπλέκτη 2x1 είναι: Y=I0S'+I1S

Κάθε λογική συνάρτηση η μεταβλητών μπορεί να υλοποιηθεί με έναν Πολυπλέκτη  $2^n x 1$ . Οι η μεταβλητές εισόδου της συνάρτησης αποτελούν τις γραμμές επιλογής του Πολυπλέκτη. Οι είσοδοι του Πολυπλέκτη επιλέγονται κατάλληλα από τον πίνακα αληθείας της συνάρτησης. Η συνάρτηση αποτελεί την έξοδο του Πολυπλέκτη.

Παράδειγμα. Η συνάρτηση τριών μεταβλητών  $F(A,B,C)=\Sigma(1,3,5,6)$  έχει τον πίνακα αληθείας :

| A | В | C | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Η συνάρτηση μπορεί να υλοποιηθεί με έναν Πολυπλέκτη 8x1 που έχει οκτώ εισόδους Ι0, Ι1, Ι2, Ι3, Ι4, Ι5, Ι6, Ι7, τρεις επιλογές S2, S1, S0 και μία έξοδο Υ.

Οι μεταβλητές εισόδου της συνάρτησης αποτελούν τις γραμμές επιλογής του Πολυπλέκτη: S2=A, S1=B, S0=C

Οι είσοδοι του Πολυπλέκτη επιλέγονται κατάλληλα από τον πίνακα αληθείας της συνάρτησης:

I0=0, I1=1, I2=0, I3=1, I4=0, I5=1 I6=1, I7=0

Η συνάρτηση αποτελεί την έξοδο του Πολυπλέκτη:

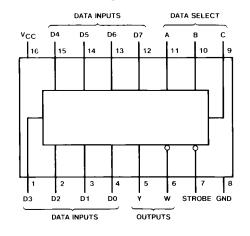

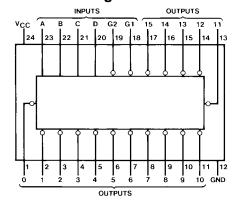

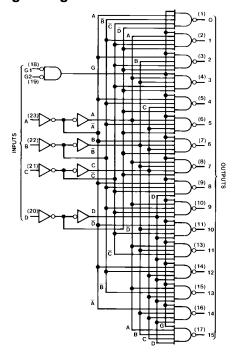

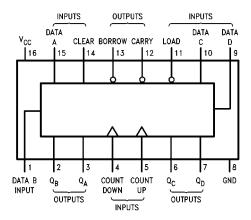

Y=F